lcd panel with transistors on the back quotation

A thin-film-transistor liquid-crystal display (TFT LCD) is a variant of a liquid-crystal display that uses thin-film-transistor technologyactive matrix LCD, in contrast to passive matrix LCDs or simple, direct-driven (i.e. with segments directly connected to electronics outside the LCD) LCDs with a few segments.

In February 1957, John Wallmark of RCA filed a patent for a thin film MOSFET. Paul K. Weimer, also of RCA implemented Wallmark"s ideas and developed the thin-film transistor (TFT) in 1962, a type of MOSFET distinct from the standard bulk MOSFET. It was made with thin films of cadmium selenide and cadmium sulfide. The idea of a TFT-based liquid-crystal display (LCD) was conceived by Bernard Lechner of RCA Laboratories in 1968. In 1971, Lechner, F. J. Marlowe, E. O. Nester and J. Tults demonstrated a 2-by-18 matrix display driven by a hybrid circuit using the dynamic scattering mode of LCDs.T. Peter Brody, J. A. Asars and G. D. Dixon at Westinghouse Research Laboratories developed a CdSe (cadmium selenide) TFT, which they used to demonstrate the first CdSe thin-film-transistor liquid-crystal display (TFT LCD).active-matrix liquid-crystal display (AM LCD) using CdSe TFTs in 1974, and then Brody coined the term "active matrix" in 1975.high-resolution and high-quality electronic visual display devices use TFT-based active matrix displays.

The liquid crystal displays used in calculators and other devices with similarly simple displays have direct-driven image elements, and therefore a voltage can be easily applied across just one segment of these types of displays without interfering with the other segments. This would be impractical for a large display, because it would have a large number of (color) picture elements (pixels), and thus it would require millions of connections, both top and bottom for each one of the three colors (red, green and blue) of every pixel. To avoid this issue, the pixels are addressed in rows and columns, reducing the connection count from millions down to thousands. The column and row wires attach to transistor switches, one for each pixel. The one-way current passing characteristic of the transistor prevents the charge that is being applied to each pixel from being drained between refreshes to a display"s image. Each pixel is a small capacitor with a layer of insulating liquid crystal sandwiched between transparent conductive ITO layers.

The circuit layout process of a TFT-LCD is very similar to that of semiconductor products. However, rather than fabricating the transistors from silicon, that is formed into a crystalline silicon wafer, they are made from a thin film of amorphous silicon that is deposited on a glass panel. The silicon layer for TFT-LCDs is typically deposited using the PECVD process.

Polycrystalline silicon is sometimes used in displays requiring higher TFT performance. Examples include small high-resolution displays such as those found in projectors or viewfinders. Amorphous silicon-based TFTs are by far the most common, due to their lower production cost, whereas polycrystalline silicon TFTs are more costly and much more difficult to produce.

The twisted nematic display is one of the oldest and frequently cheapest kind of LCD display technologies available. TN displays benefit from fast pixel response times and less smearing than other LCD display technology, but suffer from poor color reproduction and limited viewing angles, especially in the vertical direction. Colors will shift, potentially to the point of completely inverting, when viewed at an angle that is not perpendicular to the display. Modern, high end consumer products have developed methods to overcome the technology"s shortcomings, such as RTC (Response Time Compensation / Overdrive) technologies. Modern TN displays can look significantly better than older TN displays from decades earlier, but overall TN has inferior viewing angles and poor color in comparison to other technology.

Most TN panels can represent colors using only six bits per RGB channel, or 18 bit in total, and are unable to display the 16.7 million color shades (24-bit truecolor) that are available using 24-bit color. Instead, these panels display interpolated 24-bit color using a dithering method that combines adjacent pixels to simulate the desired shade. They can also use a form of temporal dithering called Frame Rate Control (FRC), which cycles between different shades with each new frame to simulate an intermediate shade. Such 18 bit panels with dithering are sometimes advertised as having "16.2 million colors". These color simulation methods are noticeable to many people and highly bothersome to some.gamut (often referred to as a percentage of the NTSC 1953 color gamut) are also due to backlighting technology. It is not uncommon for older displays to range from 10% to 26% of the NTSC color gamut, whereas other kind of displays, utilizing more complicated CCFL or LED phosphor formulations or RGB LED backlights, may extend past 100% of the NTSC color gamut, a difference quite perceivable by the human eye.

The transmittance of a pixel of an LCD panel typically does not change linearly with the applied voltage,sRGB standard for computer monitors requires a specific nonlinear dependence of the amount of emitted light as a function of the RGB value.

In-plane switching was developed by Hitachi Ltd. in 1996 to improve on the poor viewing angle and the poor color reproduction of TN panels at that time.

Initial iterations of IPS technology were characterised by slow response time and a low contrast ratio but later revisions have made marked improvements to these shortcomings. Because of its wide viewing angle and accurate color reproduction (with almost no off-angle color shift), IPS is widely employed in high-end monitors aimed at professional graphic artists, although with the recent fall in price it has been seen in the mainstream market as well. IPS technology was sold to Panasonic by Hitachi.

Most panels also support true 8-bit per channel color. These improvements came at the cost of a higher response time, initially about 50 ms. IPS panels were also extremely expensive.

IPS has since been superseded by S-IPS (Super-IPS, Hitachi Ltd. in 1998), which has all the benefits of IPS technology with the addition of improved pixel refresh timing.

In 2004, Hydis Technologies Co., Ltd licensed its AFFS patent to Japan"s Hitachi Displays. Hitachi is using AFFS to manufacture high end panels in their product line. In 2006, Hydis also licensed its AFFS to Sanyo Epson Imaging Devices Corporation.

It achieved pixel response which was fast for its time, wide viewing angles, and high contrast at the cost of brightness and color reproduction.Response Time Compensation) technologies.

Less expensive PVA panels often use dithering and FRC, whereas super-PVA (S-PVA) panels all use at least 8 bits per color component and do not use color simulation methods.BRAVIA LCD TVs offer 10-bit and xvYCC color support, for example, the Bravia X4500 series. S-PVA also offers fast response times using modern RTC technologies.

When the field is on, the liquid crystal molecules start to tilt towards the center of the sub-pixels because of the electric field; as a result, a continuous pinwheel alignment (CPA) is formed; the azimuthal angle rotates 360 degrees continuously resulting in an excellent viewing angle. The ASV mode is also called CPA mode.

A technology developed by Samsung is Super PLS, which bears similarities to IPS panels, has wider viewing angles, better image quality, increased brightness, and lower production costs. PLS technology debuted in the PC display market with the release of the Samsung S27A850 and S24A850 monitors in September 2011.

TFT dual-transistor pixel or cell technology is a reflective-display technology for use in very-low-power-consumption applications such as electronic shelf labels (ESL), digital watches, or metering. DTP involves adding a secondary transistor gate in the single TFT cell to maintain the display of a pixel during a period of 1s without loss of image or without degrading the TFT transistors over time. By slowing the refresh rate of the standard frequency from 60 Hz to 1 Hz, DTP claims to increase the power efficiency by multiple orders of magnitude.

Due to the very high cost of building TFT factories, there are few major OEM panel vendors for large display panels. The glass panel suppliers are as follows:

External consumer display devices like a TFT LCD feature one or more analog VGA, DVI, HDMI, or DisplayPort interface, with many featuring a selection of these interfaces. Inside external display devices there is a controller board that will convert the video signal using color mapping and image scaling usually employing the discrete cosine transform (DCT) in order to convert any video source like CVBS, VGA, DVI, HDMI, etc. into digital RGB at the native resolution of the display panel. In a laptop the graphics chip will directly produce a signal suitable for connection to the built-in TFT display. A control mechanism for the backlight is usually included on the same controller board.

The low level interface of STN, DSTN, or TFT display panels use either single ended TTL 5 V signal for older displays or TTL 3.3 V for slightly newer displays that transmits the pixel clock, horizontal sync, vertical sync, digital red, digital green, digital blue in parallel. Some models (for example the AT070TN92) also feature input/display enable, horizontal scan direction and vertical scan direction signals.

New and large (>15") TFT displays often use LVDS signaling that transmits the same contents as the parallel interface (Hsync, Vsync, RGB) but will put control and RGB bits into a number of serial transmission lines synchronized to a clock whose rate is equal to the pixel rate. LVDS transmits seven bits per clock per data line, with six bits being data and one bit used to signal if the other six bits need to be inverted in order to maintain DC balance. Low-cost TFT displays often have three data lines and therefore only directly support 18 bits per pixel. Upscale displays have four or five data lines to support 24 bits per pixel (truecolor) or 30 bits per pixel respectively. Panel manufacturers are slowly replacing LVDS with Internal DisplayPort and Embedded DisplayPort, which allow sixfold reduction of the number of differential pairs.

Backlight intensity is usually controlled by varying a few volts DC, or generating a PWM signal, or adjusting a potentiometer or simply fixed. This in turn controls a high-voltage (1.3 kV) DC-AC inverter or a matrix of LEDs. The method to control the intensity of LED is to pulse them with PWM which can be source of harmonic flicker.

The bare display panel will only accept a digital video signal at the resolution determined by the panel pixel matrix designed at manufacture. Some screen panels will ignore the LSB bits of the color information to present a consistent interface (8 bit -> 6 bit/color x3).

With analogue signals like VGA, the display controller also needs to perform a high speed analog to digital conversion. With digital input signals like DVI or HDMI some simple reordering of the bits is needed before feeding it to the rescaler if the input resolution doesn"t match the display panel resolution.

The statements are applicable to Merck KGaA as well as its competitors JNC Corporation (formerly Chisso Corporation) and DIC (formerly Dainippon Ink & Chemicals). All three manufacturers have agreed not to introduce any acutely toxic or mutagenic liquid crystals to the market. They cover more than 90 percent of the global liquid crystal market. The remaining market share of liquid crystals, produced primarily in China, consists of older, patent-free substances from the three leading world producers and have already been tested for toxicity by them. As a result, they can also be considered non-toxic.

Kawamoto, H. (2012). "The Inventors of TFT Active-Matrix LCD Receive the 2011 IEEE Nishizawa Medal". Journal of Display Technology. 8 (1): 3–4. Bibcode:2012JDisT...8....3K. doi:10.1109/JDT.2011.2177740. ISSN 1551-319X.

Brody, T. Peter; Asars, J. A.; Dixon, G. D. (November 1973). "A 6 × 6 inch 20 lines-per-inch liquid-crystal display panel". 20 (11): 995–1001. Bibcode:1973ITED...20..995B. doi:10.1109/T-ED.1973.17780. ISSN 0018-9383.

Richard Ahrons (2012). "Industrial Research in Microcircuitry at RCA: The Early Years, 1953–1963". 12 (1). IEEE Annals of the History of Computing: 60–73. Cite journal requires |journal= (help)

K. H. Lee; H. Y. Kim; K. H. Park; S. J. Jang; I. C. Park & J. Y. Lee (June 2006). "A Novel Outdoor Readability of Portable TFT-LCD with AFFS Technology". SID Symposium Digest of Technical Papers. AIP. 37 (1): 1079–82. doi:10.1889/1.2433159. S2CID 129569963.

Kim, Sae-Bom; Kim, Woong-Ki; Chounlamany, Vanseng; Seo, Jaehwan; Yoo, Jisu; Jo, Hun-Je; Jung, Jinho (15 August 2012). "Identification of multi-level toxicity of liquid crystal display wastewater toward Daphnia magna and Moina macrocopa". Journal of Hazardous Materials. Seoul, Korea; Laos, Lao. 227–228: 327–333. doi:10.1016/j.jhazmat.2012.05.059. PMID 22677053.

Responsible for performing installations and repairs (motors, starters, fuses, electrical power to machine etc.) for industrial equipment and machines in order to support the achievement of Nelson-Miller’s business goals and objectives:

• Perform highly diversified duties to install and maintain electrical apparatus on production machines and any other facility equipment (Screen Print, Punch Press, Steel Rule Die, Automated Machines, Turret, Laser Cutting Machines, etc.).

• Provide electrical emergency/unscheduled diagnostics, repairs of production equipment during production and performs scheduled electrical maintenance repairs of production equipment during machine service.

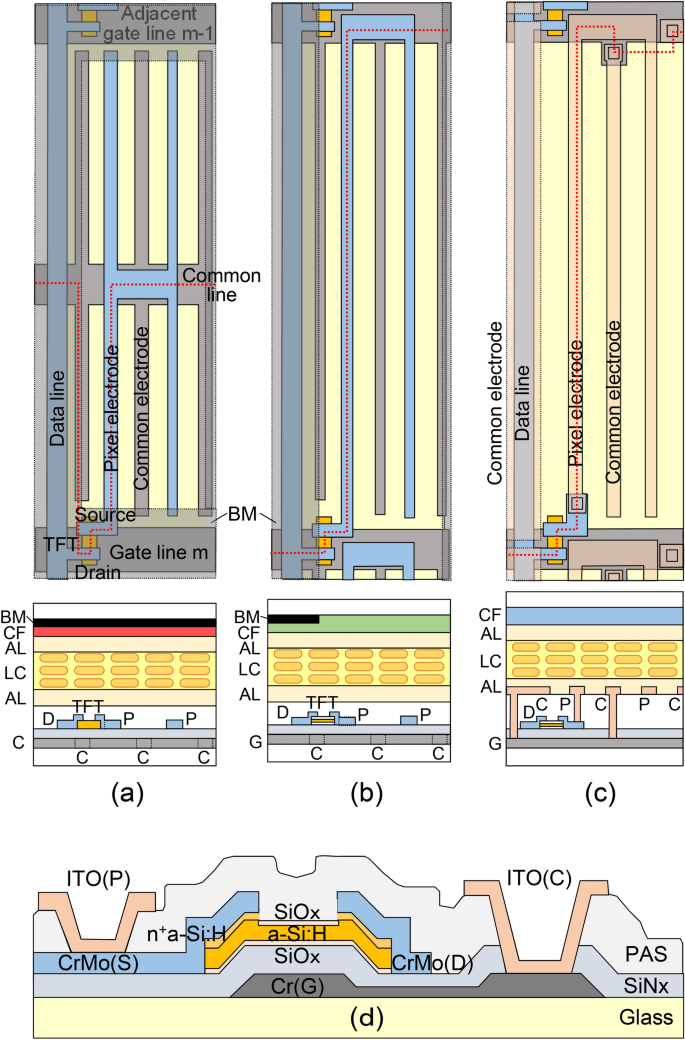

Figures 3a–d show optical and SEM (scanning electron microscopy) images of the fabricated CL and CLSE pixel structures. Each structure has the same pixel size (80 μm × 240 μm) and minimum pattern size (5 μm). As shown in Fig. 3d, the white line patterns are the ITO interdigitated pixel and common electrodes. They are well connected to the source electrode and gate line via through holes, and the common electrodes at both ends cover the underlying data lines to prevent electrical noise from being applied to the LC layer. As will be shown later, this noise shield electrode (SE) is what makes the black matrix above the data line unnecessary

Optical and SEM (scanning electron microscopy) images of fabricated (a, b) CL and (c, d) CLSE pixel structures. The five white line patterns in (d) are the ITO interdigitated pixel and common electrodes. (e) Images from the normal direction and from 50 degrees to the left and right of a 2.3-inch-diagonal display incorporating the IPS TFT-LCD panel. (f) The three-black matrix (BM) patterns (top: BM covering both gate and data lines, middle: BM covering only the data lines, and bottom: without BM) and (g) optical images of pixels without BM (left: LC on and off voltages supplied to every other data line, right: LC off voltage supplied to all data lines).

Figure 3e shows images from the normal direction and from 50 degrees to the left and right of a 2.3-inch-diagonal display incorporating the IPS TFT-LCD panel fabricated in our laboratory, (f) the three black matrix (BM) patterns (top: BM covering both gate and data lines, middle: BM covering only the data lines, and bottom: without BM), and (g) optical images of panel areas without the BM (left: LC on and off voltages supplied to every other data line, right: LC off voltage supplied to all data lines). As can be seen in the image from the normal direction, the brightness and contrast of the display area with the top BM and middle BM patterns are almost the same, but the contrast of the display area without the BM is relatively lower because of the lower darkness level of the LC off pixels indicating “HITACHI”. As shown in Fig. 3g, this is due to light leaking through the aperture between the data line and adjacent common lines. Therefore, in the CL structure, the BM on the drain line is necessary to obtain a high contrast ratio by shielding light leakage. This is the same as in the conventional structure. On the contrary, there is no light leakage along the gate line through the gaps between the gate line and edges of the pixel/common electrodes, as is clearly shown in Fig. 3g. This is a unique advantage of the CL structure because the conventional structure must shield these gaps with the BM to prevent light leakage. The suppression of light leakage along the gate line in the CL structure is due to the driving scheme (see Fig. 2b,a for a comparison with the conventional structure). During the holding period (tOFF) in the conventional structure, regardless of the pixel voltage, Vp (including Vp = 0), nonzero Vgp and Vgc are always applied to keep the TFT off, and these voltages are applied to the LC layer, inducing light leakage as reported in

Figure 4a shows the gate voltage (Vg) dependence of the panel brightness, while the inset shows that of the TFT current (transfer characteristics). The gray curves are for the conventional IPS TFT-LCD with the TFT before enhancement, the common line, and the matrix BM (MBM) shown at the top of Fig. 3f. The blue curves are for the proposed CL structure with the enhanced TFT and the stripe BM (SBM) shown in the middle of Fig. 3f. In this case, enhanced TFT characteristics were obtained by using an MNOS TFT without back-channel oxidation that was enhanced by the BTS process. In both structures, the threshold voltages for panel brightness, defined by extrapolating the straight part of the brightness curves, reflect those of the TFT transfer curves defined as Vg at a drain current of 10−12 A, and they are well matched to be 4 V and 9 V, respectively. The maximum brightness for the CL structure is 137% higher than that for the conventional structure, which is due to the increase in the aperture ratio from 38 to 52% that results from the elimination of the common line and the BM covering the gate line.

(a) Dependence of panel brightness and TFT current on gate voltage for the conventional pixel structure of 38% aperture ratio (AR) with matrix black matrix (MBM) over both drain and gate lines and proposed CL pixel structure of 52% AR with strip black matrix (SBM) over only the drain lines. Transfer characteristics before and after bias temperature stress (BTS) treatment are shown in the inset. (b) Charging and (c) holding characteristics of enhanced TFT of the CL structure with gate as a common line. Vg and Vd in the TFT ON state are 30 V and +/−7 V, respectively.

To estimate the charging and holding characteristics of the MNOS-enhanced TFT in the panel, the gate TFT ON and OFF time dependences of the panel brightness were measured (Fig. 4b,c). The charging characteristics in Fig. 4b are plotted as a function of tON at tOFF = 16.6 ms, Vg = 30 V, and Vd = ± 7 V. The holding characteristics in Fig. 4c are plotted as a function of tOFF at tON = 34 μs. 95.1% charging at tON = 34 μs and 95.3% holding at tOFF = 16.6 ms indicate that the enhanced TFT has sufficient charging and holding performance to drive a standard VGA (640 × 480 pixels) panel (the number of scanning lines is estimated as tOFF/tON = 16.6/0.034 = 488).

To confirm the driving conditions for the CL structure without the BM along the gate line (with the SBM), the tOFF dependence of the contrast ratio (CR) in the CL panel was further investigated as shown in Fig. 5a, where CR is plotted as a function of tOFF for the CL panels with the matrix BM (MBM) and the strip BM (SBM). The inset shows the brightness in the bright (Vd = 7 V) and dark (Vd = 0 V) states of the CL panel with the SBM as a function of tOFF and an optical image of the panel with tOFF = 6.4 ms. The SBM and MBM panels keep CR higher than 240 with tOFF > 16.6 ms, the frame period of a display panel without flicker being noticeable to the human eye. both panels decrease CR when tOFF is less than 16.6 ms; the CR of the SBM panel decreases faster than the CR of the MBM panel. As shown in the inset, the decrease in CR was due to the increase in dark-state brightness with decreasing tOFF as light leakage increases along the gate line. This light leakage is induced by the voltage Vgp = Vgc = VgON = 30 V applied only for 34 μs during the TFT ON (charging) state, which is 1/488th the duration, tOFF = 16.6 ms, of the TFT OFF (holding) state with Vgp = Vgc = VgOFF = 0 V, but the ratio increases with decreasing tOFF and becomes effective enough to switch on LC layer and induce light leakage. However, it should be stressed again that the CL panel with the normal holding (TFT OFF) time of 16.6 ms does not suffer from the light leakage along the gate line, so the aperture ratio can be increased by removing the BM along the gate line.

(a) Contrast ratio (CR) for CL panels with matrix BM (MBM) and stripe BM (SBM) plotted as a function of tOFF. The inset shows the brightness in the bright (Vd = 7 V) and dark (Vd = 0 V) states of the CL panel with the SBM as a function of tOFF and an optical image of the panel with tOFF = 6.4 ms. Vd (= VLC) dependence of (b) brightness and (c) contrast ratio of the CLSE panel. Insets of (b): optical images indicating the elimination of the BM from the CLSE structure (upper left) and the MBM in the conventional structure (lower right). Insets of (c): CLSE panel composed of different areas with three different pixel structures and aperture ratios (ARs), i.e., CLSE structure without BM (60%), CL structure with SBM (52%), and conventional structure with MBM (38%).

Figure 5b,c shows the Vd (= VLC) dependence of the brightness and contrast ratio of the CLSE panel without a BM along the drain line and along the gate line. As shown in the optical images in the insets of Fig. 5c, the CLSE panel has different areas with three different pixel structures and aperture ratios (ARs), i.e., the CLSE structure without the BM (60%), the CL structure with the SBM (52%), and the conventional structure with the MBM (38%). The optical images in the inset of Fig. 5b clearly indicate the elimination of the BM from the CLSE structure and the MBM in the conventional structure. The ratios of the bright area in the CLSE and conventional pixels shown in the red dotted square appear higher than the aperture ratios because the pixel and common electrodes are invisible due to the brightness. The brightness and contrast ratio in each area increase with increasing Vd; the ratios for the CLSE structure without the BM are approximately 160% those of the conventional structure with the MBM, reflecting the difference in aperture ratio.

Figure 6 indicates the effect of bias temperature stress (BTS) on the TFT characteristics. As the stressing time, tS, of the positive gate stress voltage, Vst = + 77 V, increases from 0 to 3600 s, the transfer (Id-Vg) curve shifts in the positive direction (Fig. 6a). Vth is defined as Vg at which Id = 10−12 A and ΔVth is defined as the Vth shift from the initial value via BTS. As shown in Fig. 6b, ΔVth increases logarithmically with increasing tS: ΔVth = 2.17 + 4.93 × log (tS). The mechanism behind the gate-stress-induced Vth shift is electron tunnel injection from the a-Si:H semiconductor into the SiOx gate insulator. For confirmation, ΔVth of MNOS TFTs with different SiOx thicknesses is plotted as a function of the electric field applied to the SiOx layer in Fig. 6c. Here, the thickness of the SiOx was varied (5, 10, 20, 50 nm), while the SiN thickness was fixed at 200 nm. The electric field applied to SiOx, Eox, was calculated using the following equation,

Effect of bias temperature stress (BTS) on TFT characteristics. (a) The transfer (Id–Vg) curve shifts in the positive direction with positive gate bias stress of Vst = + 77 V over the duration of 0–3600 s. (b) ΔVth, defined as the Vth shift from the initial value via BTS, increases logarithmically with increasing tS, following ΔVth = 2.17 + 4.93 × log (tS). (c) ΔVth of MNOS TFTs with different SiOx thicknesses from 5 to 50 nm as a function of the electric field applied to the SiOx layer.

where εo = 3.5 and do are the electrical permittivity and thicknesses of SiOx and εn = 7 and dn = 200 nm are those of SiN. ΔVth linearly increases at a threshold electric field at 4.6 MV/cm on the same straight line regardless of the thickness of SiOx. From these results, we concluded that the Vst-induced Vth shift mechanism is Fowler–Nordheim type tunneling injection

Figure 7a shows the effect of back-channel oxidation (BCO) and passivation (PAS) on the Id-Vg characteristics of the MNOS TFT. The Id-Vg curve with Vth = 5.1 V is further enhanced to Vth = 10.9 V after BCO, although there is a slight degradation of the slope of the current increase in the sub-threshold region. The slope recovers after PAS without any change to the enhanced characteristics

(a) Effect of back-channel oxidation (BCO) and passivation (PAS) on Id–Vg characteristics of MNOS TFT. (b) Vth and Vth standard deviation, σVth, after BTS and after BCO without BTS treatments and (c) SiOX thickness as a function of position along gate-line, x.

The advantage of BCO over BTS is the uniformity of the enhanced characteristics; Fig. 7b shows the distribution of the enhanced Vth as a function of position along gate-line, x, for the MNOS TFTs connected with a 90-mm-long gate line in the TFT substrate after BTS and BCO treatments. The average value of Vth and the standard deviation, σVth, for pristine TFTs before BTS or BCO, are 5.1 V and 0.35 V, respectively. After BCO, Vth is uniformly enhanced, with an average Vth = 11 V and σVth = 0.4 V without increasing σVth. On the other hand, after BTS, Vth is nonuniformly enhanced with an average Vth = 9.3 V and σVth of 1.4 V. In particular, Vth increases linearly as a function of position along gate-line, x. As the gate SiOx thickness linearly decreases, from (54 nm) to (47 nm) with increasing x as shown in Fig. 7c, the increase in ΔVth after BTS with x is due to increase in the electric field applied to SiOx as shown in Fig. 6c and Eq. 1.

It has been shown that the Vth of the MNOS TFT is independent of the gate SiOx thickness when the thickness is more than 5 nm8a, Vth of the MNOS TFT with the BCO treatment becomes almost independent of the BCO SiOx thickness. As shown in the inset, the thickness of BCO SiOx composed of oxidized a-Si:H linearly increases with BCO processing time, and the Vth increase almost saturates at a BCO SiOx thickness greater than 5 nm. Therefore, the enhanced MNOS TFT after BCO has a uniformly high Vth that is robust to thickness fluctuations of the gate and BCO SiOx layers. BCO also has an advantage over BTS in terms of the stability of Vth as shown in Fig. 8b, which plots the annealing time dependence of Vth for BCO and BTS. In this experiment, the stoichiometry (x) of the gate SiOx was 1.78 for BTS and 1.78 and 1.9 for BCO. The annealing temperature in the N2 atmosphere was 200 °C. In the case of BTS, Vth decreased to the pristine value after approximately 5 h of annealing, while Vth decreased more slowly in the case of BCO. In particular, the annealing time required for Vth to fall to 7 V was 7.5 times longer than that of BTS. Increasing the stoichiometry (x) of the gate SiOx dramatically improved the BCO-enhanced Vth to as much as 11 V, which was stably maintained after 24 h of annealing at 200 °C.

(a) Dependence of Vth on thickness of back-channel oxidized (BCO) SiOX. The inset shows the SiOx thickness dependence on the BCO process time for RF powers of 200 W and 500 W. (b) Stability of Vth as a function of annealing time for three different TFTs with gate SiOx stoichiometry, x = 1.78 and bias temperature stress (BTS), x = 1.78 and BCO, and x = 1.9 and BCO. The temperature of annealing in the N2 atmosphere was 200 °C. (c) Band diagram of back-channel oxidized MNOS TFT. The red arrows show the electric dipoles at the SiOX/a-Si:H and a-Si:H/BCO SiOX interfaces.

A schematic band model for the MNOS TFT with the BCO treatment and the sectional structure of the interface between the a-Si:H and gate and BCO SiOx are shown in Fig. 8c. The uniformly high Vth that is independent of SiOx thickness is due to the dipoles generated at the channel and back-channel interfaces between a-Si:H and SiOx8 of reference

To create an LCD, you take two pieces ofpolarized glass. A special polymer that creates microscopic grooves in the surface is rubbed on the side of the glass that does not have the polarizing film on it. The grooves must be in the same direction as the polarizing film. You then add a coating of nematic liquid crystals to one of the filters. The grooves will cause the first layer of molecules to align with the filter"s orientation. Then add the second piece of glass with the polarizing film at a right angle to the first piece. Each successive layer of TN molecules will gradually twist until the uppermost layer is at a 90-degree angle to the bottom, matching the polarized glass filters.

As light strikes the first filter, it is polarized. The molecules in each layer then guide the light they receive to the next layer. As the light passes through the liquid crystal layers, the molecules also change the light"s plane of vibration to match their own angle. When the light reaches the far side of the liquid crystal substance, it vibrates at the same angle as the final layer of molecules. If the final layer is matched up with the second polarized glass filter, then the light will pass through.

If we apply an electric charge to liquid crystal molecules, they untwist. When they straighten out, they change the angle of the light passing through them so that it no longer matches the angle of the top polarizing filter. Consequently, no light can pass through that area of the LCD, which makes that area darker than the surrounding areas.

Building a simple LCD is easier than you think. Your start with the sandwich of glass and liquid crystals described above and add two transparent electrodes to it. For example, imagine that you want to create the simplest possible LCD with just a single rectangular electrode on it. The layers would look like this:

The LCD needed to do this job is very basic. It has a mirror (A) in back, which makes it reflective. Then, we add a piece of glass (B) with a polarizing film on the bottom side, and a common electrode plane (C) made of indium-tin oxide on top. A common electrode plane covers the entire area of the LCD. Above that is the layer of liquid crystal substance (D). Next comes another piece of glass (E) with an electrode in the shape of the rectangle on the bottom and, on top, another polarizing film (F), at a right angle to the first one.

The electrode is hooked up to a power source like a battery. When there is no current, light entering through the front of the LCD will simply hit the mirror and bounce right back out. But when the battery supplies current to the electrodes, the liquid crystals between the common-plane electrode and the electrode shaped like a rectangle untwist and block the light in that region from passing through. That makes the LCD show the rectangle as a black area.

A PCN may only apply to specific orderable part numbers in this datasheet. Please refer to the corresponding PCN to see the exact orderable part number(s) affected.

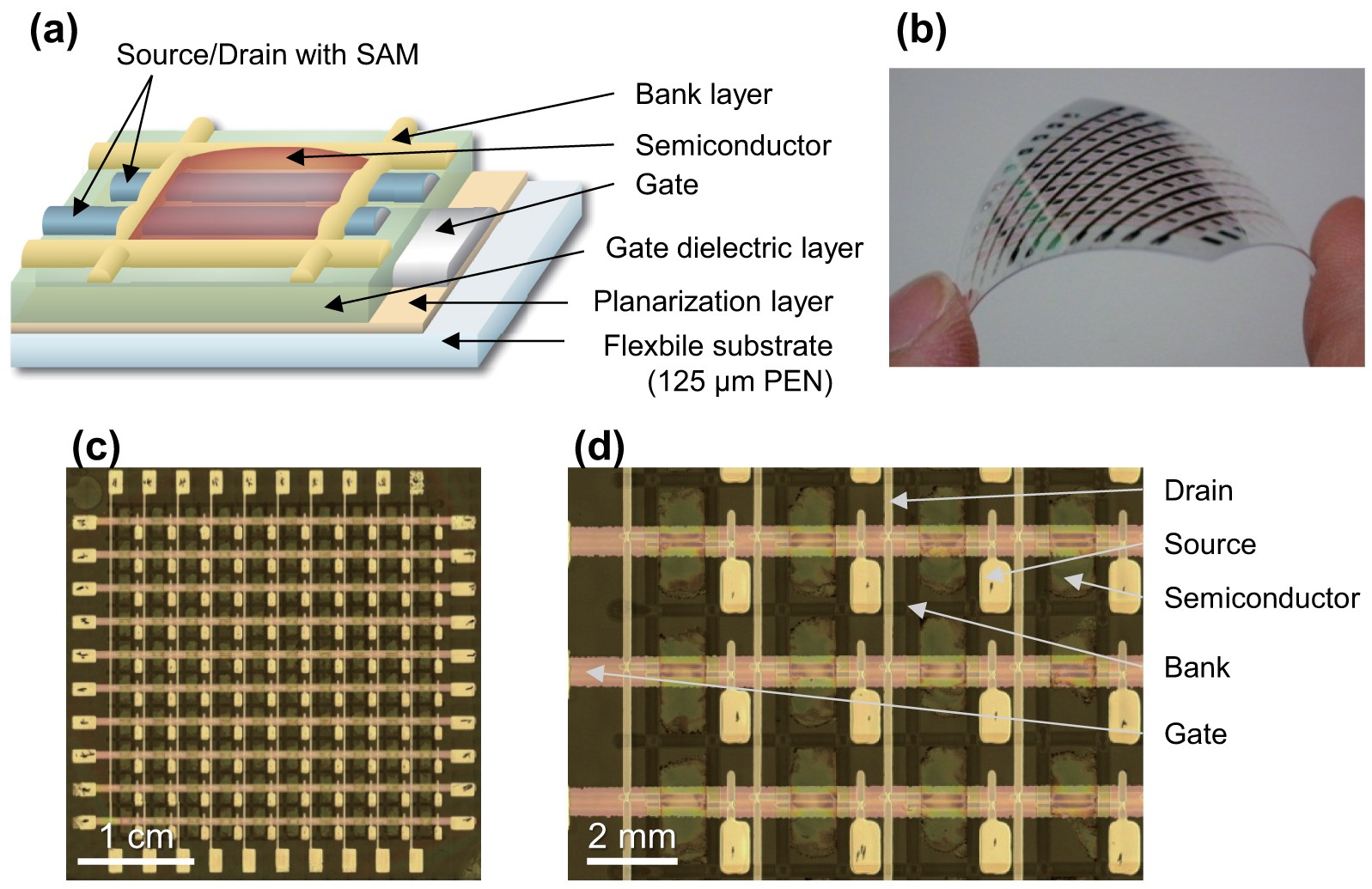

Chances are, you are reading these words on a smartphone or computer screen. For around the last 10 years, these types of screens have been based on a display technology composed of so-called thin film transistors. These are inorganic transistors which require very little power, and they have proven themselves very capable, given their widespread adoption—but they have some limits which researchers have been busy trying to overcome.

"We explore new ways to improve upon thin film transistors, such as new designs or new methods of manufacture," said Gyo Kitahara, a PhD student from the Department of Applied Physics. "Organic thin film transistors, for example, have a bright future in LCD screen devices. Compared to the inorganic kind currently used, we expect the organic kind to be useful in low-cost, large-area, lightweight and wearable electronic products, especially by using printing-based production technologies."

The idea of organic thin film transistors itself is not new, but the ability to print such devices, which would allow for a design revolution, has eluded industry and academics, until now. Professor Tatsuo Hasegawa of the Department of Applied Physics, Kitahara, and their team came up with a way to print organic semiconductor films, the basis of these transistors, on a special surface that is highly solution-repellent, or lyophobic. This means ordinarily the surface would repel the materials required to print the structure of the transistor, which seems counterintuitive as to why such a surface would be useful at all. But lyophobic surfaces are responsible for creating transistor structures that are finely tuned for high performance. So how did the researchers overcome their repellent nature?

"We made use of a fluidic property you probably see every time you wash your hands with soap," said Kitahara. "Soap bubbles can hold a shape by lowering the surface tension of liquid. We presume that the soap-film mechanism should be effective for formation of a thin liquid layer on lyophobic surfaces in spite of the repellent forces. Solid semiconductor films can be formed and grown via the formation of thin liquid layers during the printing processes."

With this hurdle of how to print organic transistors overcome, other researchers can build on the team"s findings and find ways to scale this method up. With a proliferation of large, flexible, or wearable devices, Hasegawa"s team dreams of seeing a convergence between the real world and virtual world in ways we"ve never seen before.

"After having experimented by trial and error, we eventually found that the use of a special U-shaped metal-film pattern seems to be effective for uniform film growth thanks to the way it creates a thin liquid layer on lyophobic surfaces," said Kitahara. "We anticipated the results beforehand to some extent, but the success of these findings was finally demonstrated and obtained after overcoming several difficulties, which brought great pleasure and happiness to me."

This website is using a security service to protect itself from online attacks. The action you just performed triggered the security solution. There are several actions that could trigger this block including submitting a certain word or phrase, a SQL command or malformed data.

Liquid-crystal display (LCD) was invented in 1964 at RCA Laboratories in Princeton, NJ. In 1970, twisted-nematic (TN) mode of operation was discovered, which gave LCD the first commercial success. The LCD manufacturers supplied small-size displays to portable products such as digital watches and pocket calculators. In 1988, Sharp Corporation demonstrated a 14-in. active-matrix full-color full-motion display using a TFT (thin-film-transistor) array. Observing this, Japan launched a true LCD industry. Large-size displays were first supplied to personal computers and then to television receivers. In the second half of 1990s, the industry has moved to Korea and Taiwan.

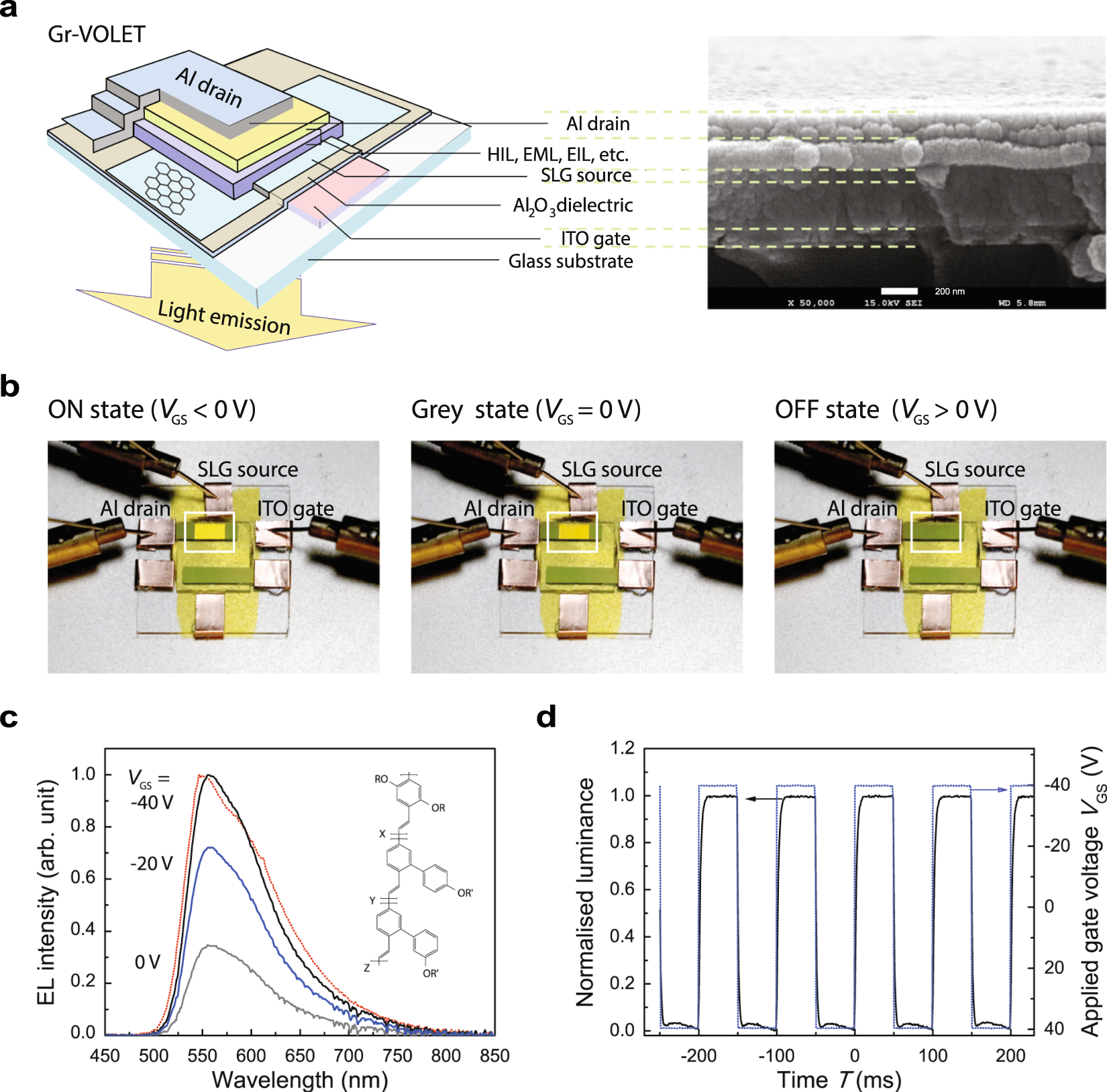

Zoom InZoom OutReset image sizeFigure 1. (a) Schematic VOFET cross section, (b) photography of a sample of V-OFETs on a 5 × 5"" substrate, (c) comparison of VOFET and OTFT layouts.

We developed a fabrication procedure for V-OFETs which is fully compatible with state-of-the-art display backplane technologies. In this regard, our work differs substantially from previous reports about vertical organic transistors where sophisticated fabrication methods have been employed which cannot seamlessly be adopted in a production line for high-resolution displays. Such processes are: shadow mask patterning [11], lift-off [12], nm-scale lithography [10, 15], and unconventional electrode or gate insulator materials [9, 13]. We only employ well-established fabrication techniques for large area and high throughput industrial processes, such as conventional photolithography, wet and/or dry etching are employed [22–24]. Scalable processes such as sputtering or CVD can be used for the preparation of the gate insulator. In particular, in this work we use a gate dielectric with a specific capacitance of 50 nF cm−2 (hybrid dielectrics composed of 25 nm of Al2O3 and 30 nm of the fluoropolymer CYTOP), which is in the typical range applied in backplane manufacturing. Source and Drain electrodes are composed of Au (thickness of 40 nm) and are patterned by photolithography followed by a wet-etching in KI/I2 (denoted as standard etchant gold). The gate electrode is made of Al (thickness of 200 nm) and it is patterned by photolithograhy and wet etching. The SD-insulator is a highly cross-linked photoresist (NLOF2020) with a thickness between 400 and 700 nm. The thickness of the semiconductor layer is 25 nm. Finally, the semiconductor film is patterned by reactive ion etching using oxygen [24]. All processing steps are performed under ambient conditions (except the vacuum deposition steps) and at process temperatures ≤120 °C.

Zoom InZoom OutReset image sizeFigure 2. (a) Transfer curve for a V-OFET (W = 20 μm) at VDS = −10 V approaching the saturation, (b) comparison of the transfer curves in the linear regime of V-OFET devices on a 5 × 5"" substrate at VDS = −5 V. Different colors represent the transfer curves of the individual transistors.

Besides an outstanding FET performance (on/off-ratio and on-current density) and possibility to process these devices at temperatures ≤120 °C, V-OFETs show as well excellent device uniformity and stability, demonstrating that this technology is suited for display integration. Focusing on device uniformity, we can report excellent threshold voltage Vth and on-current uniformity on a full 5 × 5"" substrate of 0.41 V and 4.3%, respectively (table 1 and figure 2(b)). This high level of uniformity is achieved because only scalable processes such as photolithography and solution-coating are used. Furthermore, we could identify the uniformity of the gate insulator thickness and the metal line width as the main uniformity limitation for our process. Hence, it is apparent that V-OFET uniformity will be further improved when transferring the technology to a mass production environment. Finally, we report device stability data in the bottom part of table 1. Especially looking at bias stress stability under illumination, the V-OFET technology provides a clear advantage over a-IGZO due to the low absorption coefficient of the OSC.

Summary of V-OFET uniformity and stability data. Measurement conditions are: V-OFET (p-type): VDS = −0.1 V, VGS = +/−15 V, T = 20 °C.V-OFETOn-current (std. dev.)

V-OFET design paradigms—Due to the vertical stacking of gate, source and drain electrodes, V-OFETs obey different scaling laws than their planar counterparts. The knowledge on the transistor scaling behavior is of utmost importance for high-resolution displays for two reasons: first, the limited area for the transistors due to the demand on the storage capacitor or the aspect ratio of the pixel, and second, the transistor capacitance which is strongly affecting the dynamic properties of each pixel in a display. The existence of the gate-drain capacitance of the switch transistor in an AM backplane, gives rise to the so-called voltage-kick-back effect [25]—a rapid discharging of the storage capacitor when the transistor is switched off—being one of the biggest issues for high-resolution displays. As we will see, V-OFETs offer both, a reduced transistor footprint and a smaller gate-drain overlap capacitance, which in turn makes the V-OFET technology interesting for ultra-high resolution display applications.

From figure 3(a) it is apparent that vertical FETs have always a lower total gate area than planar FETs for the considered parameters. For typical display parameters OL = LW = 3.5 μm, the gate area of the V-OFET is only 66% of the gate area for the horizontal FET, corresponding to a reduction in gate capacitance of one third. The area ratio can be further reduced to 35% in case of a more aggressive design with OL = 2 μm and LW = 1 μm. In figure 3(b), the total gate area of V-OFETs and of planar FETs with different channel lengths L (OL = LW = 3.5 μm) is shown as function of the channel width W. As it can be seen, even when scaling the channel length down to 3 μm, the area ratio remains lower than 80%. This reduction of gate area for V-OFETs is related to the vertical channel configuration as well as to the fact that all edges of the source electrode contribute to the channel width.

So far we compared the total gate area for vertical and horizontal FETs. However, this does not directly translate into a gate capacitance gain since only the overlap area between gate and source/drain electrodes contribute the FET capacitance. In figure 3(c), we show the ratio of the device capacitance of vertical and horizontal FETs for a typical value of W = 6 μm and a channel lengthL = 5 μm for the planar FET. As it can be seen, the ratio between the vertical and the horizontal FET strongly depends on the line width and to a lesser extent on the overlay accuracy. In particular, there is no advantage of the vertical configuration for LW ≥ 6 μm and OL ≥ 4 μm. However, this case is not relevant for high-resolution displays which require small line width and overlay. For application-relevant dimensions such as LW ≤ 4 μm and OL ≤ 4 μm, the V-OFET provides a reduction of gate capacitance of at least 20%. This reduction of capacitance becomes increasingly important when LW andOL are scaled down as it is needed for higher display resolutions (≥4k2k).

We would finally like to give an example of typical values for an AMOLED display backplane considering the two layouts in figure 1(c). These are optimized for a design OL = LW = 3.5 μm and characterized by W = 7 μm and L = 5 μm. Assuming a specific gate capacitance of 20 nF cm−2, the device capacitance would be only 12 fF for the V-OFET to be compared to 17 fF for the corresponding planar FET. Furthermore, the reader should keep in mind that due to its short channel, a V-OFET with W = 6 μm provides significantly more on-current density than the corresponding planar OFET [22].

Finally, we would like to highlight the importance of this capacitance reduction for the pixel design and performance of a high resolution display. The capacitance reduction affects the dynamic behavior of the switching transistor in two ways. Firstly, the lower total capacitance leads to a faster response (shorter raise time of current) of the switching transistor during the programming phase of the pixel. However, the capacitance reduction due to smaller overlay does not translate one-to-one into a raise time reduction, since in a real display the raise time is also governed by the metal line resistance and the overlay capacitance of the supply lines. Still, the reduced transistor capacitance reduces the overall capacitive load of the supply lines. The second and probably most important effect of the reduced capacitance of the switching transistor concerns the turning-off behavior of the switching transistor at the end of the programming phase. As mentioned above, the gate-drain overlay capacitance leads to a rapid discharging of the storage capacitor and hence a loss of the brightness information programmed onto the storage capacitor when the switching transistor is abruptly switched off. This effect is known as voltage-kick-back effect [25] and it is determined by the ratio of the storage capacitance to the gate-drain capacitance. In fact, the suppression of this kick-back effect is vital for the fabrication of high resolution displays and it is one of the main reasons why self-aligned transistor architectures are preferred for such display. In this context, a reduction of the transistor capacitance by more than 40% enabled by the vertical configuration is essential in order to effectively suppress the kick-back effect.

Ms.Josey

Ms.Josey

Ms.Josey

Ms.Josey