lcd panel timing controller factory

Different displays use different types of TCONs. In this article we will be talking about TCONs for the IT market: LCD (Liquid Crystal Display) notebook PCs and monitors.

An LCD panel has millions of Red, Green, and Blue (RGB) liquid crystals that are used to block a white backlight when electrical voltage is applied to them. High voltage signals to each individual pixel control how much of the backlight to block. A white display means nothing is being blocked. A black display means all three colors are blocked at maximum effort.

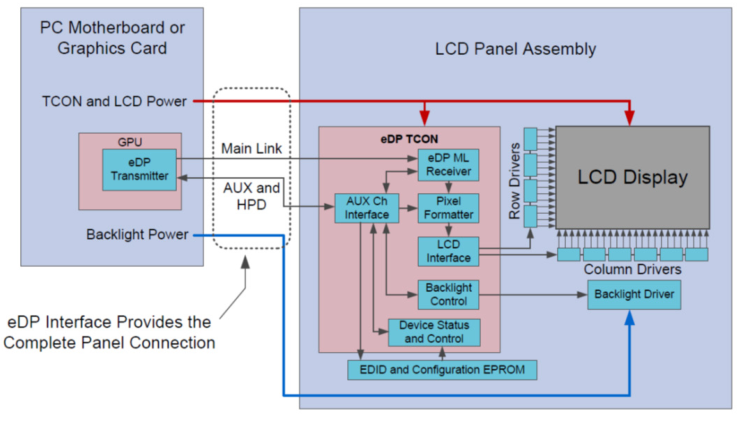

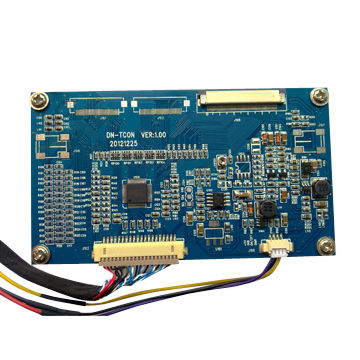

TCONS direct the high voltage driver chips that move the color filters and are usually found on a circuit board that sits below the glass panel (Fig. 1).

eDP connections are fast, use few wires, and are flexible for size, bandwidth and adding features eDP provides all panel connections in one plug, including power, data, and control signals. This is Analogix’s specialty.

While the GPU is responsible for transforming mathematical equations into individual pixels and frames, a TCON takes the individual frames generated by the GPU, corrects for color and brightness, then sends out parts of the image to each individual driver at the panel’s specific timing.

The human eye has an incredible dynamic range. That means we can see both very dark images and very bright images, at the same time. However, neither camera sensors nor display panels can display that range. Your camera generates HDR images by using images from multiple exposures to combine the brightest and darkest parts of the picture. This increases the contrast (dynamic range) between light and dark, pulling out details from darkened or washed out areas.

HDR accurately maps real world color and luminance to a display panel. VESA DisplayHDR™ standard specifies HDR quality, including luminance, color gamut, bit depth, and rise time.

Display panels have difficulty displaying a wide range of brightness. Normal sunlight can reach 10,000 nits, but the backlight on most notebooks today is around 250 nits

VESA DisplayHDR requires the panel to meet minimum brightness, contrast, and color. No panel can reach 10,000nits of natural light. The brightest a 250nit notebook panel can produce is 250nits and any image above 250nits is washed out. Also, no details from 250 nits to 10,000nits can be seen.

The HDR400 specifications require a dimmable backlight which helps with both producing darker blacks and lowering the power consumption. Tone mapping is used to map the whole range of 10,000 nits down to what the panel can handle, so the details can be seen. Tone mapping does not increase the brightness of the panel; it only makes the details visible.

VESA DisplayHDR600 Requires local dimming. No LCD panel can reach the VESA DisplayHDR600 requirement of 6000:1 contrast ratio. However, this can be overcome with local dimming.

For example, a 750:1 contrast panel requires 8 different backlight power settings to reach 6000:1 contrast ratio. However, unless there are thousands of separate regions, local dimming always produces halos around the bright areas. In order to reduce the halos, the following are recommended:

Monitors can use a direct backlight with many regions. An extra layer of liquid crystal can be used to dim the backlight at a specific location but this often results in a panel that is too thick for a notebook.

Notebook backlights use LEDs on the edge of the panel to reduce panel thickness. These can be on 1 side, 2 sides, or all 4 sides. Each edge adds to cost and bezel size.

Global Dimming Power Savings - Figure 6 shows a 15.6” UHD panel with 400nit maximum brightness. Figure 7 shows a comparison of backlight power consumption values between 400nit, 50nit and, respectively 5nit.

The primary goal of color management is to obtain a good match across color devices; for example, the colors of one frame of a video should appear the same on a computer LCD monitor, on a TV screen, and as a printed poster. Color management helps to achieve the same appearance on all of these devices, provided the devices are capable of delivering the needed color intensities. Color management cannot guarantee identical color reproduction, as this is rarely possible, but it can at least give more control over any changes which may occur.

A PC in HDR and SDR modes use different color gamut but the same screen. Dual-panel phones and notebooks need the color of the two sides to match perfectly. Graphic artists for web sites, movies, video games, etc., need to know what they are creating looks the same on their screen as on their customers’ screens.

As panels improve, the color space of new panels may exceed the color space from Windows. This results in displays which look oversaturated. There is a trend towards low blue light or “night shift” panels, while still retaining color accuracy for the other colors. Today, low blue light panels are created by measuring each individual panel, then hoping that the yield is high enough.

Analogix’s Advanced Color Blocking (ACB) technology is used to create consistent image quality across different panels and change color space for different usage modes (Fig. 8). It allows for 3D color gamut rotation in the optical color domain rather than the RGB domain and color space change on the fly, such as color mapping of BT.2020 source to sRGB or DCI-P3 panels. It includes LUT shadow registers and hardware transition calculations (to smooth changes).

Color conversion in the TCON can dynamically and continuously adjust the incoming signal from the GPU for a low blue light color space. This way, no individual panel measurement is needed and yields should increase. While this can also be done by the GPU itself, that takes GPU bandwidth and 500x more power.

Panel Self-Refresh (PSR) – frame buffer in a TCON can maintain a display image without receiving video data from the CPU. For a still image, this allows the GPU to enter a low-power state and the eDP main link to turn off. Allowing the GPU to power down between display updates will save significant power and extend battery life.

Panel Self-Refresh with Selective Update (PSR2) is a superset of the panel self-refresh feature and it allows the transmission of modified areas within a video frame with obvious benefits when watching a movie or playing a game. PSR2 identifies when only a portion of the screen is static, which is a selective update. In PSR2, when the full screen is static, the refresh rate can be lowered for further power savings as done by Intel Low Refresh Rate (LRR). Intel LRR lowers the refresh rate by changing pixel clock or by changing vertical blank depending on the scenario such as idle, playing video, browsing, etc. All Analogix TCONs support Intel LRR.

In-Cell Touch embeds the touch function in the display itself, the panel including all the touch sensors, controllers, and needed processing. This simplifies the production process and reduces weight and reflection by removing the cover glass. It also allows for thinner bezels as there is no need for daughter cards and no separate wires for touch, as well as lighter devices as the cover glass is removed.

Analogix has pioneered the in-cell touch notebook panel TCONs. About 15% of notebooks support touch and we expect the touch attach rate to increase as more active pen support is introduced.

Digital View’s SVX-1920v3 is a full featured LCD controller that is a suitable fit for an extensive range of professional display applications. This is an advanced LCD controller that is ideal for use with high resolution

Digital View"s ALR-1400v2 is a multi-purpose LCD controller that was designed for industrial LCD monitors and can be used for a number of industrial and commercial display applications. Features: ∙ Compact Design ∙

Digital View’s ALR-1920-120 is a multi-purpose LCD controller board with a comprehensive selection of built-in features and control options. This solution is compatible with 120Hz panels with up to 1920x1200 resolution.

The 4169900XX-3 / SP-1600 Controller is end of life (EOL) as of September 15, 2017. The last time buy (LTB) date is/was October 1, 2017. The suggested replacement is the SP-1920. Features: ∙ 10-bit ∙ LVDS

Digital View’s SVH-1920v2 LCD controller is the updated replacement for the SVH-1920. This newer version includes the same signal inputs and mountings as the original with the addition of an eDP panel connection and increased

The 4171400XX-3 / DVS-1600 Controller is end of life (EOL) as of September 15, 2017. The last time buy (LTB) date is/was October 1, 2017. The suggested replacement is the SP-1920. Features: ∙ 10-bit ∙ LVDS

The 4169901XX-3 / HE-1600 Controller is end of life (EOL) as of September 15, 2017. The last time buy (LTB) date is/was October 1, 2017. The suggested replacement is the SP-1920. Features: ∙ 10-bit ∙ LVDS

Digital View’s HE-1920v2 is the replacement for the HE-1920. It is a harsh environment LCD controller with ceramic capacitors and unmatched durability. The HE-1920v2 has a conformal coating layer that preserves the components

The HLR-1920 by Digital View is a compact, wide temperature LCD controller great for general purpose solutions. It is compatible with LCD panels up to 1920x1200 resolution. The HLR-1920 features low signal latency from input

The 4172200XX-3 / AVP-1600 Controller is end of life (EOL) as of September 15, 2017. The last time buy (LTB) date is/was October 1, 2017. The suggested replacement is the SP-1920. Features: ∙ 10-bit ∙ LVDS

Digital View’s SVX-2560 is an advanced LVDS and eDP panel LCD controller. It works with LCD panel resolutions up to 2560x1600 and 1920x1920 and is compatible with video signals up to 2560x1600. Features: ∙ LCD

Digital View"s SVX-4096 is an advanced LCD controller ideal for 4K LCDs. It is compatible with LCD and OLED panel resolutions up to 4096x2160 and video signals up to 4096x2160. Because it is a 4K LCD controller, it is an ideal

The Digital View HX-4096 is a harsh environment 4k LCD controller. It supports video signals up to 4096 x 2160 and LCD panel resolutions up to 4096 x 2160. Because of its conformal coating and extended temperature range,

Digital View’s HSP-1920 is the durable, harsh environment version of the SP-1920 LCD controller. It is supports input and panel activity for video signals up to 1920x1200. The built-in H.246 failover media player makes

Digital View’s ALT-1920 is a compact, general solution LCD controller that covers three popular input formats including HDMI, Analog RGB (VGA), and DisplayPort. It is equipped with ceramic capacitors for improved reliability

The Digital View SP-4096 is an easy-to-use controller board for 4k LCDs. It supports LCD panels and video output of up to 4096 x 2160 resolution. Because of its high resolution and excellent reliability, this 4k LCD controller

The Digital View HSP-4096 is the harsh environment version of the SP-4096 and includes a conformal coating that provides increased resistance to the elements. It supports video signals up to 4096 x 2160 and LCD panel resolutions

The Digital View SVX-4096-120 is an advanced controller board that can support both LCD and OLED panels up to 4096 x 2160 resolution. Because of its super high resolution, this 4k controller board is ideal for commercial

The Digital View DT-4096 is a compact and easy-to-use controller board that supports LCD panels up to 4096 x 2160 resolution. Because of its extensive image control options and super high resolution, this 4k controller

The timing controller (“TCON”) receives image data and converts the format for the source drivers’ input and also generates controlling signals for gate and source drivers.

Himax have a complete product line and leading technology on Tcon panel for Automotive, Tablet, NB, Monitor, TV, public or industrial displays. We also provide high resolution, high frame rate, low power consumption, high speed transmitter interface technology that help improve image quality. In addition, we are dedicated to new display technology for OLED and uLED, which continue to provide customers with innovative and forward-looking solutions.

(Hong Kong – 30 June 2006) Solomon Systech Limited is proud to launch their TFT LCD timing controller, SSD2900, which supports high resolution – SXGA (1280 x 1024) and UXGA (1600 x 1200) TFT-LCD monitors. This simple but specific IC specializes in its integrated dual LVDS (Low-Voltage Differential Signaling) receivers and RSDS (Reduced Swing Differential Signaling) transmitter.

SSD2900 supports 18/24 bit-per-pixel LVDS input and transmits 18/24 bit-per-pixel RSDS data. The LVDS and RSDS are low voltage swing interfaces for low EMI solution. SSD2900 has on-chip spread spectrum controller which provides total solution to EMI. It reduces EMI by tolerating spread spectrum interface at LVDS input, whereas the spread spectrum controller at RSDS output varies the clock to wider the spectrum in frequency domain with center spread +/- 0.25% of nominal frequency at 2kHz. In addition, the embedded timing controller operates in DE-only mode which provides accurate timing control signals for source/gate drivers. Bandwidth of one channel LVDS is 25-85MHz, whereas maximum output RSDS bandwidth is 85MHz. Moreover, SSD2900 supports virtual 8-bit color depth in FRC mode. Its low power core operates from 3.0V to 3.6V. The usage of SSD2900 is simply hardware, no application software and command required.

T-Con board is commonly referred to as timing controller board or controller board or control board. It is found in all LCD TVs. Panel repair factory is one of the top suppliers of T-Con board to LCD TV manufacturers and repair agencies around the world. Panel repair factory T-Con board effectively controls the gate signals. It is also the main source for driving TFT-LCD. T-Con boards possess a frame rate converter that ranges between 60 hertz to 120 hertz. Panel repair factory T-Con board is capable of developing accurate voltages depending upon the type of panel used in the LCD TV. It functions with the voltage directed to it from the motherboard. It is made up of special drivers and comprises of top quality circuits, Gamma and high signal input. It is capable of producing clear and accurate colour displayed on LCD TV. The special FPGA ensures stable and trustworthy operational performance. The high Technology interpolation algorithms provide brilliant font and image display in perfect synchronicity. It comes with a powerful power protection mechanism which protects the device from electric short circuits, and damages caused by excessive heat.

The DP627 is a panel timing controller (Tcon) developed specifically for a PC Direct Drive Monitor (DDM). It includes a DisplayPortTM receiver and supports display resolutions up to 1920 x 1200 (Full HD) with up to 30 bit color. It is designed to be mounted on the LCD panel, elliminating the seperate monitor controller board within the monitor to reduce monitor size and cost.

The DP627 provides pixel data through a mini-LVDS interface with programmable timing to support a variety of LCD panel designs. The device includes audio support through both I2S and S/PDIF digital outputs. The DP627 de-spreads the DisplayPort SSC Link clock, and can also add SSC on the mini-LVDS output.

Hantronix TFT LCDs will deliver a vibrant, high contrast user interface to any application. Our TFT displays are available in a wide range of sizes, and are easy to incorporate into any design. We offer the most popular and cost-effective Amorphous Silicon Thin Film Transistor or a-SiTFT panels. This application note discusses how to drive a TFT LCD using widely available microprocessors.

Note that some small, lower end panels may not have all of the electronics included with them because of size or cost restraints. Some panels have a simple row and column interface. Some may need an external timing controller. Some have a processor bus type Interface.

Depending on internal circuitry demands, some panels may include a few other signals, such as a reset line. Determining how to drive such simple signals is usually straightforward.

Many LCD controllers, including those integrated into microcontrollers, will directly drive the signals shown in Figure 1. This means that the biggest obstacle to quickly getting an image on the screen is generating the appropriate signal timing. The LCD controller is responsible for generating the timing; however software must be written to correctly program the controller for the specific LCD model.

An LCD panel comprises a matrix of pixels (picture elements), divided into red, green, and blue "sub-pix-els". Each sub-pixel is driven by a small transistor. Typically, LCD panels have internal row and column drivers, much like DRAM. A row is selected by the row driver, then the column driver sequences through each of the columns. After each of the columns has been written, the row driver selects the next row and the process repeats. The VSYNC signal resets both row and column drivers to the upper left pixel. The HSYNC causes the row driver to step to the new row. The clock sequences the column driver through each of the pixels, with each clock edge latching data values for the red, green, and blue sub-pixels. These values drive a form of D/A converter to store an electrical charge in a capacitor in each sub-pixel which controls the drive of the transistor; this in turn controls the brightness of the sub-pixel. A red-green-blue color mask is used to filter the light from each sub-pixel to form its corresponding color.

Like a DRAM, an LCD panel must be constantly refreshed or the image will fade. Most TFT LCD panels work when refreshed around 60 Hz. The imagedata is usually held in a section of main memory called a frame Buffer.

Each location in the frame buffer corresponds to a pixel on the LCD. The value in the location determines the color displayed for that pixel. See Figure 2. The size of the frame buffer depends on two things: the number of locations needed, and the size of each location.

The total number of locations needed is determined by the panel resolution. For instance, the resolution of the Hantronix HDA350-2G panel is 320 × 240 pixels. Therefore 320 × 240 = 76,800 memory locations will be needed in the frame buffer „ one for each pixel.

TFT panels typically have an input of at least 6 bits of red data, 6 bits of green data, and 6 bits of blue data. A panel with 6 red, 6 green, and 6 blue data lines is termed a 6-bit panel. If the processor or LCD controller doesn"t drive as many data lines as the panel requires, use the data line configuration shown in Figure 3 or Figure 5.

The Valid Data time (THd) is equal to the number of pixels in the horizontal direction, in this case 320. From the Timing Table we see that the typical value for the HSYNC pulse (THp) is 12, and the typical number of total clocks per line is 400.

The HLT-1920 LCD controller is the harsher environment version of the ALT-1920. It combines three of the most popular video input formats, HDMI, Analog RGB (VGA) and DisplayPort in a compact general purpose solution for LCD panels up to 1920x1200 resolution. One of the key features of this compact highly reliable controller is the low signal latency from input signal to panel output signal. In addition the controller uses ceramic capacitors to improve reliability and lifetime at elevated temperatures.

The ALT-1920 combines three of the most popular input formats, HDMI, Analog RGB (VGA) and DisplayPort in a compact general purpose solution for LCD panels up to 1920x1200 resolution. It is an excellent board to start with for panel and project evaluation as well as ideal for many display products. One of the key features of this compact highly reliable controller is the low signal latency from input signal to panel output signal. In addition the controller now uses ceramic capacitors to further improve reliability.

ESP chips can generate various kinds of timings that needed by common LCDs on the market, like SPI LCD, I80 LCD (a.k.a Intel 8080 parallel LCD), RGB/SRGB LCD, I2C LCD, etc. The esp_lcd component is officially to support those LCDs with a group of universal APIs across chips.

In esp_lcd, an LCD panel is represented by esp_lcd_panel_handle_t, which plays the role of an abstract frame buffer, regardless of the frame memory is allocated inside ESP chip or in external LCD controller. Based on the location of the frame buffer and the hardware connection interface, the LCD panel drivers are mainly grouped into the following categories:

Controller based LCD driver involves multiple steps to get a panel handle, like bus allocation, IO device registration and controller driver install. The frame buffer is located in the controller’s internal GRAM (Graphical RAM). ESP-IDF provides only a limited number of LCD controller drivers out of the box (e.g. ST7789, SSD1306), More Controller Based LCD Drivers are maintained in the Espressif Component Registry

RGB Interfaced LCD - is based on a group of specific synchronous signals indicating where to start and stop a frame. The frame buffer is allocated on the ESP side. The driver install steps are much simplified because we don’t need to install any IO interface driver in this case.

LCD Panel IO Operations - provides a set of APIs to operate the LCD panel, like turning on/off the display, setting the orientation, etc. These operations are common for either controller-based LCD panel driver or RGB LCD panel driver.

esp_lcd_panel_io_spi_config_t::dc_gpio_num: Sets the gpio number for the DC signal line (some LCD calls this RS line). The LCD driver will use this GPIO to switch between sending command and sending data.

esp_lcd_panel_io_spi_config_t::cs_gpio_num: Sets the gpio number for the CS signal line. The LCD driver will use this GPIO to select the LCD chip. If the SPI bus only has one device attached (i.e. this LCD), you can set the gpio number to -1 to occupy the bus exclusively.

esp_lcd_panel_io_spi_config_t::pclk_hz sets the frequency of the pixel clock, in Hz. The value should not exceed the range recommended in the LCD spec.

esp_lcd_panel_io_spi_config_t::spi_mode sets the SPI mode. The LCD driver will use this mode to communicate with the LCD. For the meaning of the SPI mode, please refer to the SPI Master API doc.

esp_lcd_panel_io_spi_config_t::lcd_cmd_bits and esp_lcd_panel_io_spi_config_t::lcd_param_bits set the bit width of the command and parameter that recognized by the LCD controller chip. This is chip specific, you should refer to your LCD spec in advance.

esp_lcd_panel_io_spi_config_t::trans_queue_depth sets the depth of the SPI transaction queue. A bigger value means more transactions can be queued up, but it also consumes more memory.

Install the LCD controller driver. The LCD controller driver is responsible for sending the commands and parameters to the LCD controller chip. In this step, you need to specify the SPI IO device handle that allocated in the last step, and some panel specific configurations:

esp_lcd_panel_dev_config_t::bits_per_pixel sets the bit width of the pixel color data. The LCD driver will use this value to calculate the number of bytes to send to the LCD controller chip.

esp_lcd_panel_io_i2c_config_t::dev_addr sets the I2C device address of the LCD controller chip. The LCD driver will use this address to communicate with the LCD controller chip.

esp_lcd_panel_io_i2c_config_t::lcd_cmd_bits and esp_lcd_panel_io_i2c_config_t::lcd_param_bits set the bit width of the command and parameter that recognized by the LCD controller chip. This is chip specific, you should refer to your LCD spec in advance.

Install the LCD controller driver. The LCD controller driver is responsible for sending the commands and parameters to the LCD controller chip. In this step, you need to specify the I2C IO device handle that allocated in the last step, and some panel specific configurations:

esp_lcd_panel_dev_config_t::bits_per_pixel sets the bit width of the pixel color data. The LCD driver will use this value to calculate the number of bytes to send to the LCD controller chip.

esp_lcd_i80_bus_config_t::data_gpio_nums is the array of the GPIO number of the data bus. The number of GPIOs should be equal to the esp_lcd_i80_bus_config_t::bus_width value.

esp_lcd_panel_io_i80_config_t::pclk_hz sets the pixel clock frequency in Hz. Higher pixel clock frequency will result in higher refresh rate, but may cause flickering if the DMA bandwidth is not sufficient or the LCD controller chip does not support high pixel clock frequency.

esp_lcd_panel_io_i80_config_t::lcd_cmd_bits and esp_lcd_panel_io_i80_config_t::lcd_param_bits set the bit width of the command and parameter that recognized by the LCD controller chip. This is chip specific, you should refer to your LCD spec in advance.

esp_lcd_panel_io_i80_config_t::trans_queue_depth sets the maximum number of transactions that can be queued in the LCD IO device. A bigger value means more transactions can be queued up, but it also consumes more memory.

Install the LCD controller driver. The LCD controller driver is responsible for sending the commands and parameters to the LCD controller chip. In this step, you need to specify the I80 IO device handle that allocated in the last step, and some panel specific configurations:

esp_lcd_panel_dev_config_t::bits_per_pixel sets the bit width of the pixel color data. The LCD driver will use this value to calculate the number of bytes to send to the LCD controller chip.

esp_lcd_panel_dev_config_t::reset_gpio_num sets the GPIO number of the reset pin. If the LCD controller chip does not have a reset pin, you can set this value to -1.

More LCD panel drivers and touch drivers are available in IDF Component Registry. The list of available and planned drivers with links is in this table.

esp_lcd_rgb_panel_config_t::clk_src selects the clock source for the RGB LCD controller. The available clock sources are listed in lcd_clock_source_t.

esp_lcd_rgb_panel_config_t::bits_per_pixel set the number of bits per pixel. This is different from esp_lcd_rgb_panel_config_t::data_width. By default, if you set this field to 0, the driver will automatically adjust the bpp to the esp_lcd_rgb_panel_config_t::data_width. But in some cases, these two value must be different. For example, a Serial RGB interface LCD only needs 8 data lines, but the color width can reach to RGB888, i.e. the esp_lcd_rgb_panel_config_t::bits_per_pixel should be set to 24.

esp_lcd_rgb_panel_config_t::sram_trans_align and esp_lcd_rgb_panel_config_t::psram_trans_align set the alignment of the allocated frame buffer. Internally, the DMA transfer ability will adjust against these alignment values. A higher alignment value can lead to a bigger DMA burst size. Please note, the alignment value must be a power of 2.

esp_lcd_rgb_panel_config_t::bounce_buffer_size_px set the size of bounce buffer. This is only necessary for a so-called “bounce buffer” mode. Please refer to Bounce Buffer with Single PSRAM Frame Buffer for more information.

esp_lcd_rgb_panel_config_t::timings sets the LCD panel specific timing parameters. All required parameters are listed in the esp_lcd_rgb_timing_t, including the LCD resolution and blanking porches. Please fill them according to the datasheet of your LCD.

esp_lcd_rgb_panel_config_t::fb_in_psram sets whether to allocate the frame buffer from PSRAM or not. Please refer to Single Frame Buffer in PSRAM for more information.

esp_lcd_rgb_panel_config_t::num_fbs sets the number of frame buffers allocated by the driver. For backward compatibility, 0 means to allocate one frame buffer. Please use esp_lcd_rgb_panel_config_t::no_fb if you don’t want to allocate any frame buffer.

Most of the time, the RGB LCD driver should maintain at least one screen sized frame buffer. According to the number and location of the frame buffer, the driver provides several different buffer modes.

This is the default and simplest and you don’t have to specify flags or bounce buffer options. A frame buffer is allocated from the internal memory. The frame data is read out by DMA to the LCD verbatim. It needs no CPU intervention to function, but it has the downside that it uses up a fair bit of the limited amount of internal memory.

If you have PSRAM and want to store the frame buffer there rather than in the limited internal memory, the LCD peripheral will use EDMA to fetch frame data directly from the PSRAM, bypassing the internal cache. You can enable this feature by setting the esp_lcd_rgb_panel_config_t::fb_in_psram to true. The downside of this is that when both the CPU as well as EDMA need access to the PSRAM, the bandwidth will be shared between them, that is, EDMA gets half and the CPUs get the other half. If there’re other peripherals using EDMA as well, with a high enough pixel clock this can lead to starvation of the LCD peripheral, leading to display corruption. However, if the pixel clock is low enough for this not to be an issue, this is a solution that uses almost no CPU intervention.

The PSRAM shares the same SPI bus with the main Flash (the one stores your firmware binary). At one time, there only be one consumer of the SPI bus. When you also use the main flash to serve your file system (e.g. SPIFFS), the bandwidth of the underlying SPI bus will also be shared, leading to display corruption. You can use esp_lcd_rgb_panel_set_pclk() to update the pixel clock frequency to a lower value.

To avoid tearing effect, using two screen sized frame buffers is the easiest approach. In this mode, the frame buffer can only be allocated from PSRAM, because of the limited internal memory. The frame buffer that the CPU write to and the frame buffer that the EDMA read from are guaranteed to be different and independent. The EDMA will only switch between the two frame buffers when the previous write operation is finished and the current frame has been sent to the LCD. The downside of this mode is that, you have to maintain the synchronization between the two frame buffers.

This mode allocates two so-called bounce buffers from the internal memory, and a main frame buffer that is still in PSRAM. This mode is selected by setting the esp_lcd_rgb_panel_config_t::fb_in_psram flag and additionally specifying a non-zero esp_lcd_rgb_panel_config_t::bounce_buffer_size_px value. The bounce buffers only need to be large enough to hold a few lines of display data, which is significantly less than the main frame buffer. The LCD peripheral will use DMA to read data from one of the bounce buffers, and meanwhile an interrupt routine will use the CPU DCache to copy data from the main PSRAM frame buffer into the other bounce buffer. Once the LCD peripheral has finished reading the bounce buffer, the two buffers change place and the CPU can fill the others. The advantage of this mode is that, you can achieve higher pixel clock frequency. As the bounce buffers are larger than the FIFOs in the EDMA path, this method is also more robust against short bandwidth spikes. The downside is a major increase in CPU use and the LCD CAN’T work if we disable the cache of the external memory, via e.g. OTA or NVS write to the main flash.

Note that this mode also allows for a esp_lcd_rgb_panel_config_t::bb_invalidate_cache flag to be set. Enabling this frees up the cache lines after they’re used to read out the frame buffer data from PSRAM, but it may lead to slight corruption if the other core writes data to the frame buffer at the exact time the cache lines are freed up. (Technically, a write to the frame buffer can be ignored if it falls between the cache writeback and the cache invalidate calls.)

This mode is similar to the Bounce Buffer with Single PSRAM Frame Buffer, but there is no PSRAM frame buffer initialized by the LCD driver. Instead, the user supplies a callback function that is responsible for filling the bounce buffers. As this driver does not care where the written pixels come from, this allows for the callback doing e.g. on-the-fly conversion from a smaller, 8-bit-per-pixel PSRAM frame buffer to an 16-bit LCD, or even procedurally-generated frame-buffer-less graphics. This option is selected by setting the esp_lcd_rgb_panel_config_t::no_fb flag and supplying a esp_lcd_rgb_panel_config_t::bounce_buffer_size_px value. And then register the esp_lcd_rgb_panel_event_callbacks_t::on_bounce_empty callback by calling esp_lcd_rgb_panel_register_event_callbacks().

It should never happen in a well-designed embedded application, but it can in theory be possible that the DMA cannot deliver data as fast as the LCD consumes it. In the ESP32-S3 hardware, this leads to the LCD simply outputting dummy bytes while DMA waits for data. If we were to run DMA in a stream fashion, this would mean a de-sync between the LCD address the DMA reads the data for and the LCD address the LCD peripheral thinks it outputs data for, leading to a permanently shifted image.

In order to stop this from happening, you can either enable the CONFIG_LCD_RGB_RESTART_IN_VSYNC option, so the driver can restart the DMA in the VBlank interrupt automatically or call esp_lcd_rgb_panel_restart() to restart the DMA manually. Note esp_lcd_rgb_panel_restart() doesn’t restart the DMA immediately, the DMA will still be restarted in the next VSYNC event.

esp_lcd_panel_draw_bitmap() is the most significant function, that will do the magic to draw the user provided color buffer to the LCD screen, where the draw window is also configurable.

Commands sent by this function are short, so they are sent using polling transactions. The function does not return before the command transfer is completed. If any queued transactions sent by esp_lcd_panel_io_tx_color() are still pending when this function is called, this function will wait until they are finished and the queue is empty before sending the command(s).

Commands sent by this function are short, so they are sent using polling transactions. The function does not return before the command transfer is completed. If any queued transactions sent by esp_lcd_panel_io_tx_color() are still pending when this function is called, this function will wait until they are finished and the queue is empty before sending the command(s).

This function can be useful when the LCD controller is out of sync with the DMA because of insufficient bandwidth. To save the screen from a permanent shift, you can call this function to restart the LCD DMA.

If CONFIG_LCD_RGB_RESTART_IN_VSYNC is enabled, you don’t need to call this function manually, because the restart job will be done automatically in the VSYNC event handler.

If this flag is enabled, the host only refresh the frame buffer when esp_lcd_panel_draw_bitmap is called. This is useful when the LCD screen has a GRAM and can refresh the LCD by itself.

Ms.Josey

Ms.Josey

Ms.Josey

Ms.Josey