fpga lcd display manufacturer

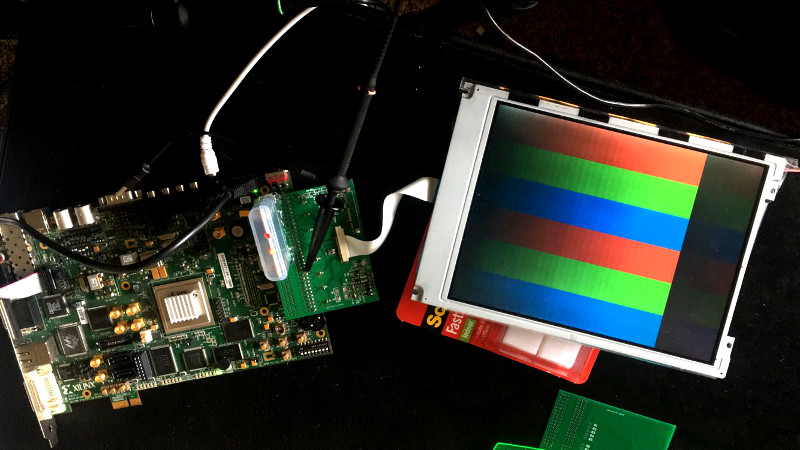

If you’re reading this article on a desktop or laptop computer, you’re probably staring at millions of pixels on a TFT LCD display. TFT became a dominant technology due to its picture quality and fast response times, but it’s not the only way to build an LCD. There are cheaper technologies, such as STN and its color variant, CSTN. They’re rarely used nowadays, but [Wenting Zhang] had one lying around and wanted to take a crack at driving it.

[Wenting] instead grabbed an FPGA and got to work. Driving displays can be taxing for small microcontrollers, so an FPGA is always a great choice when working on such projects. They’re easily capable of generating whatever weird and wacky signals are required, and can generate many such signals in parallel without breaking a sweat.

As an Industrial LCD module distributor, we can supply a wide range of TFT LCDs in many sizes. Common resolutions are QVGA, VGA, SVGA and XGA. Wide aspect ratio displays are also available in many similar sizes and resolutions such as WQVGA, WVGA, WSVGA, and WXGA.

Our industrial LCD suppliers are manufacturers with different capabilities specially designed for a wide variety of industrial applications. High-brightness, sunlight readability and long life product guarantees are some of the special features available.

Get in touch to work closely with one of our LCD Solutions Specialists to determine the perfect display for your project. We can also recommend and supply the proper LCD controller board, inverter, LED driver, cables, touch screen, or other associated enhancement.

As a KOE distributor, we supply their full line of LCDs. KOE"s display line-up consists of industrial grade, long life, flat panel display products, encompassing standard TFT-LCD modules, panel specific LCD controllers, and other custom products.

Outdoor Readable TFT Displays have the ability to maintain a high quality display image even in direct sunlight. These displays are commonly found in bright light or outdoor environments, and used in applications such as POS terminals and kiosks.

Higher Definition TFT Displays have high-quality image detail such as color gamuts and color reproduction. These displays also have a high contrast ratio and brightness. Higher definition TFT displays are commonly found in consumer products such as computer monitors and smartphones.

Rugged+ TFT Displays are designed specifically to function in harsh environmental conditions. KOE"s lineup of Rugged+ displays feature high brightness, long-life LED backlights, and ensure reliable operation even in extreme temperatures. These displays can be found in industrial, medical, marine, automotive, and aerospace applications.

Wide Format TFT Displays were enabled by traditional TFT technology and the migration of IPS technology to industrial and commercial displays. These displays are ideally suited for human machine interface applications, such as front panel instrument consoles and control system designs and applications.

Standard Format TFT Displays provide inherent quality and exceptional optical performance. These displays can be used in a wide variety of applications, such as navigation systems, home automation, process control, security systems, and media players.

KOE"s line of STN LCD Displays provide simple, easy to use, and cost-effective display solutions for your application. These displays feature a simple GUI for instrumentation, process control, and security systems. Some of these displays feature integrated display controllers and memory, which allow for microcontrollers to be used in order to enable the design of cost-effective user interfaces and systems.

Their LCD products range in size, resolution, "ruggedness" and more. Edge can help you find the appropriate display for your project, along with all the necessary components.

Lincoln Technology Solutions is a Design Services and LCD Integration Company, focused on creating solutions with unrivaled optical performance. We have in-house engineering expertise in all disciplines with prototype manufacturing in NC, USA. We pride ourselves in offering the flexibility, agility, and creativity that you cannot find with other companies that offer similar services. All of our solutions focus on solving our customer’s challenges with a cost-effective, manufacturable product.

In addition, we also offer turnkey production of our LCD solutions through our wholly owned ISO 9001 Certified LCD factory in Shenzhen, China and our PCB and subassembly assembly partner in Thailand. We will create the LCD’s you need so you can provide the solutions that your customers demand.

David previously worked for various large-scale corporations, and throughout his career at these different businesses, he realized that he wanted to branch out to be able to bring his own creativeness and innovation to the LCD and PCB industry. The ability to make a difference and build the best displays in the world is what keeps him motivated, along with spending time with his family, playing ice hockey, and enjoying a relaxing day on the lake.

LTS allows Jacob to not only work on fascinating display projects in various industries, such as medical, automotive and broadcast, but to also travel around the world to visit clients, as well as oversee our factory in Shenzhen, China. If Jacob is not in the office working, he is most likely travelling with family to the mountains and beach, riding motorcycles on the Blue Ridge Parkway, or enjoying various kinds of classical and modern art ranging from photography to sculpture.

Jesse’s drive comes from being able to work with highly motivated individuals, who are all working toward the common goal of producing world class displays. He also believes that LTS is a great company because we are an agile organization with the ability to react quickly and exceed customer expectations. When he is not busy here at our Cary office, Jesse enjoys spending time with his family, travelling, and being outdoors as much as possible.

Lincoln Technology Solutions allows Chelsea to fulfill her career aspirations, and she appreciates that the company recognizes the competence and potential of not only herself, but all their employees. The team dynamic, company benefits and the passion that emerges from the individuals here at LTS are some of the things she values most in working here at LTS. Outside of the display industry, you can find Chelsea swimming, biking, and even though they can truly scare her, she loves watching horror movies!

The life span of traditional LCD screens is between 40,000 and 60,000 hours, and the more recent popular OLED screens have a life span of about 30,000 hours. If you look at the phone for an average of 3 hours a day, it can also last 10,000 days, or 27 years, which is far more than the average user’s replacement cycle.

OLED display technology, which uses a very thin coating of organic material and a glass substrate (or flexible organic substrate) that emits light when an electric current is passed through it.

Nowadays, OLED screen has become the standard for high-end smartphones, compared with the traditional LCD technology, it is not only thinner, lower energy consumption, high brightness, can display pure black, faster response time, but also can be made into a curved screen, giving people a different visual impact

Why under-screen fingerprint recognition can only be used in OLED screen? This is because it is relatively “soft”, OLED in the construction of only two layers of thin film and glass or plastic substrate, and through the OLED material self-lighting characteristics, can be without backlight module and color filter, also do not need the general LCD panel filling liquid crystal process, can achieve 0.5-1.8mm thickness. Nowadays, most of the under-screen fingerprint recognition is optical fingerprint program, so relatively in the use of optical fingerprint program, OLED screen will be more suitable.

Why can’t under-screen fingerprint recognition be used in LCD screen? This is because it is relatively “hard”, the working principle of LCD is mainly composed of two parallel glass plate, between the two layers of glass plate and then by the liquid crystal layer and polarizer, color filter layer and so on material composition. In simple terms, LCD is the need for backlight irradiation to display, so is the result of LCD screen than OLED screen thicker, light transmission is weaker, not conducive to the use of under-screen fingerprint identification.

Since OLED screen can use under-screen fingerprint recognition, why do not all cell phone manufacturers use OLED screen? This involves the advantages and disadvantages of LCD screens and OLED screens.

LCD screen, although temporarily can not use under-screen fingerprint recognition, but, LCD screen is also the advantages of OLED can not be comparable, there is a natural DC dimming more eye protection, color is also natural, drawing people prefer LCD, screen life compared to OLED long, but also not easy to change color, also do not have to worry about using a long time after the problem of burning screen, which is also the reason why LCD loyal users like it.

In addition, LCD screen does not stimulate the human eye, will not cause eye fatigue, especially open eye protection mode filtering blue light, less damage to the eyes. oled screen will leave residual shadows, eye damage, even dimming can not be completely avoided.

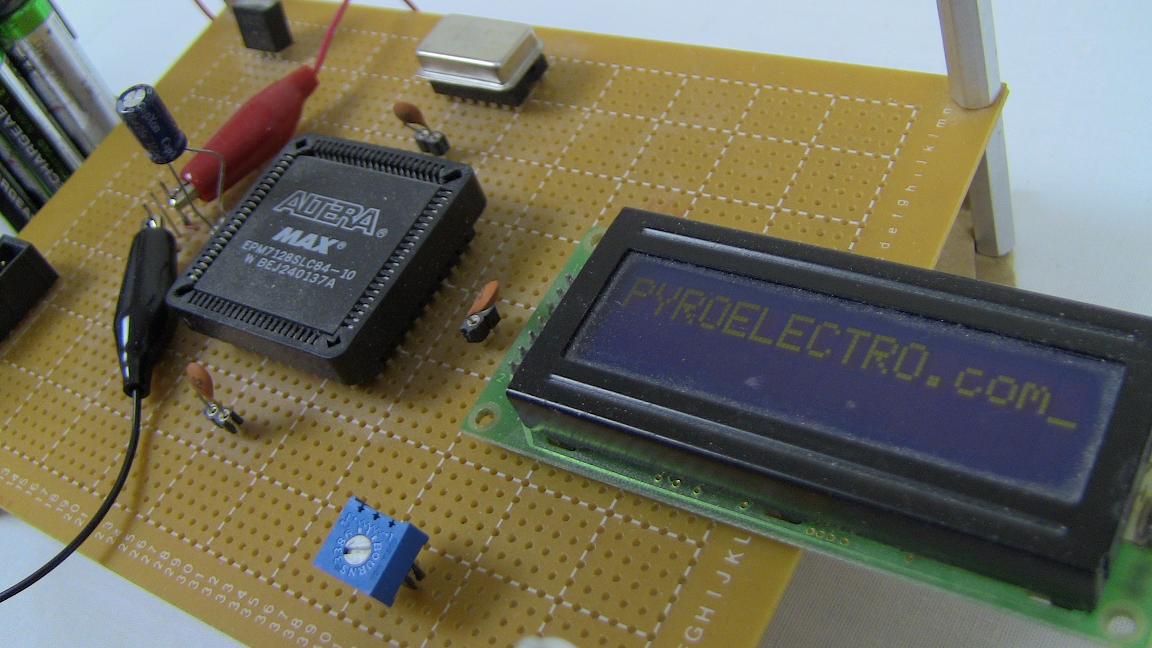

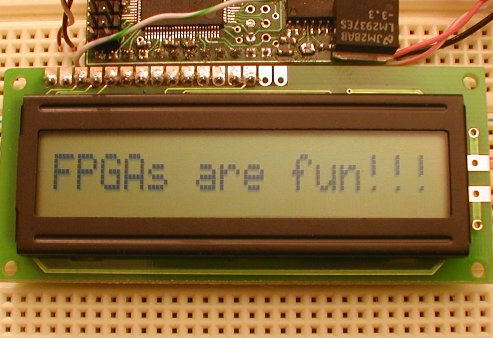

Adding a character liquid crystal display (LCD) to an FPGA project is a simple and inexpensive way to get your project talking. In this post I discuss interfacing an FPGA with garden-variety generic 1602 LCD like the one pictured nearby. These alphanumeric displays include an integrated HD44780-compatible controller with a parallel interface that enables you to send data in ASCII format one byte at a time. The output is two lines of 16 characters each on a fixed dot matrix grid. They"re cheap as chips (as my English friends say) and perfect for displaying measurements, results of calculations and any other simple messages.

My objective here was to develop a reusable Verilog module that could be dropped in to multiple FPGA projects and handle the low-level communication with the LCD. As part of an effort to make the Verilog as platform independent as possible, I developed and tested the module on two different boards. First is an Olimex ICE40HX8K-EVB board using the Project Icestorm workflow. (I discuss the board and Project Icestorm in an earlier post here: iCE40 and the IceStorm Open Source FPGA Workflow.) Second is an Arrow BeMicro CV board featuring an Intel/Altera 5CEFA2F23C8N Cyclone V, developed using Quartus 15.0.

The Hitachi HD44780 LCD controller has been around for decades. I don"t have an exact year of release, but a quick search has it turning up in catalogs and magazines by the early-to-mid-eighties. Somewhere along the line Hitachi stopped making them, but compatible replacements exist including the Sunplus SPLC780, the Samsung KS0066U and the Sitronics ST7066U. While not all small text displays are HD44780-compatible, the instruction set and interface for the controller have become something of a standard.

Both 5v and 3.3v displays are available. While it"s technically possible to interface a 5v version, I don"t have any appetite for letting 5v devices get too close to the 3.3v IO pins on my FPGA board, so I"m of course using a 3.3v version.

Configuring these displays is reasonably easy and there is a lot of raw material online to help get a project started. The fact that they"ve been around so long means there are tutorials available for every imaginable microcontroller. They"ve even shown up on some Xilinx and Altera training and development boards over the years.

I think I"ve got the timing pretty-well demystified and I"ll provide some detail further in this posting. But at a high level I can say that it"s very helpful to remember that the timing requirements from the datasheets are minimum requirements. You don"t have to try to achieve these exact time values. In fact, unless you have an application that needs to squeeze every nanosecond of performance out of the display, you can save yourself a lot of headache by building in some nice buffer around the minimum timings.

Five of the pins are dedicated to power, including a contrast control for adjusting the backlighting. Vss (ground) and Vdd (positive supply) are the main power for the logic. A and K are positive and ground to the backlight. The V0 pin adjusts the contrast to the display. Most setups use a 10k potentiometer on the contrast pin. You can tie it straight to ground through a 1K to 4K resistor, but the contrast is pretty sensitive and if you use a potentiometer you"ll probably be happier.

Three of the pins are dedicated to control signals. The RS (register select) is used to indicate whether data on the bus is a character (RS=1) or an instruction (RS=0). The E (enable) pin is toggled on and off to enter the data. The R/W (read/write) pin switches between read (R/W=1) and write (R/W=0). R/W is frequently tied to ground and the LCD is treated as a write only device. (My setup has R/W tied to ground and the FPGA and Verilog ignore it.)

The remaining eight pins are the data bus. As noted, data on the bus can either be a character or an instruction. Characters include standard ASCII codes for the numbers 0-9, letters a-z and A-Z, and many of the general standard ASCII punctuation and symbols such as !, ?, #, and $. Beyond those characters, the LCD will have additional characters depending on the manufacturer of the board and the version of the controller. The controller can also manage user-defined custom characters.

At the highest level, controlling the display can be seen as a simple process of pushing a sequence of instructions and characters through by setting up the RS pin and the DB0-7 pins one byte at a time while toggling the E pin on and off to tell the controller as each byte is ready.

Before data or instructions can be written to the controller, an initialization sequence must be executed that configures the controller and makes sure it"s ready to receive input. The HD44780 does run through a version of the initialization when it first powers up, but there are a few problems with that routine. The hardware initialization is somewhat fragile and very dependent on the circuit"s power supply. It also sets the controller to a default that might not be the desired state. Best practice looks to be including initialization in the design. For my own use, I have the FPGA drive the full initialization sequence on startup and have also tied the sequence to a push button on my board for a soft reset.

Steps 2,3 and 4 all load the same instruction to the controller. Once RS and D[0-7] are set on the FPGA it is not necessary to keep resetting them - all that is needed is to bring the enable pin high and low at the appropriate times.

Step 8 configures the Entry Mode which determines what the controller does as it receives new characters. The setting here fills in text from left to right while the display itself stays still. There are multiple options.

To implement the initialization sequence, I again use a state machine to step through the process. I actually combine the initialization and operating phases into one 26-step state machine (code further below). Of course, my solution is only one of many possible approaches. In researching for this project and hunting up examples of FPGAs driving LCDs, I found tremendous variety in the ways that people setup their state machines and manage the timing. It"s certainly worth looking around for inspiration.

The final steps in making a usable LCD driver involve reconfiguring the module to process incoming data (rather than just displaying the letter "H" in the notional code) and establishing some type of handshaking.

Slightly trickier is the idea of establishing communication between the LCD driver module and the hypothetical other module producing the data. The LCD driver needs to know when there is fresh data available to be written to the display. Likewise, since the LCD driver needs considerable time to process a byte of data, the data producing module needs to know when the LCD driver is ready. In the code below you"ll see that I addressed these two parallel needs with a "data_ready" input bit and a "busy_flag" output bit.

In states 23-25, which comprise the portion of the state machine that actually writes data to the LCD, state 23 will idle until the data_ready bit goes high. Once the bit goes high, the module sets its own internal tracking bit called "start" to high, sets the busy_flag output high, and starts processing the incoming data. The busy_flag and start bits remain high until the process is complete.

Below is the Verilog code for the full LCD driver module. This module has been tested with a hello world demonstration. I"m not displaying the full demo, but you can download it here: Verilog LCD Hello World Demonstration. The demonstration adds a ROM with the ASCII codes for Hello World and a controller that interfaces with the LCD module to feed one character at a time.

Project IceStorm is the first, and currently only, fully open source workflow for FPGA programming. Here, the software and hardware are discussed and a small sample project implemented.

The panel uses a 30-pin connector (which plugs into a port on the mainboard). The 30 pin connector then splits into two: one set of wires goes to the inverter for the backlight, and the other set containing the LVDS & EDID wires goes to the PCB on the LCD panel.

FPD-Link is a high speed digital video interface that is used to transmit video from the GPU (laptop/tablet/TV motherboard) to the display panel. FPD-Link uses LVDS (Low Voltage Differential Signalling), which transmits bits of data as differences in voltages between the 2 twisted pair wires. LVDS reduces the generation of electromagnetic noise, and due to the twisted pair cables and differential signalling, is resistant to common mode noise as well. Note that most literature refers to FPD-Link as "LVDS", although LVDS is just the electrical standard, and FPD-Link defines the signalling/packet structure.

From what I"ve read here and here, FPD-Link is being phased out and replaced by embedded Display Port. As panel resolutions increase, LVDS requires multiple channels (eg at 1080p60, FPD-Link requires around 4 or 5 channels @ ~135Mhz), but eDP can do with only 1 or 2 channels, and much higher signalling rates (1.6, 2.7, 5.4 Gbits). eDP would be interesting to try, but it would need a more expensive FPGA that has Gigabit transceivers.

I then turned to the the laptop mainboard, since if there was a LVDS transmitter, I could find a way to route the signals from the FPGA to the transmitter. I managed to find schematics for the laptop, but the LVDS signals were being routed directly from the Intel Chipset. I checked the datasheet for the chipset (an Intel 965 Express), and it confirmed that the Chipset was infact generating LVDS. This meant that it wouldn"t be possible to tap the data lines of any LVDS transmitter, and I would need to find a way of generating it.

I was searching for LCD addon boards (PMOD, FMC etc.) to see how the signalling & conversion is implemented, when I found a forum post detailing how Avnet"s 7-inch Zed Touch Display Kit generates a LVDS signal using the Zynq"s TMDS33 outputs.

The LCD panel uses a CFL backlight (it"s from an old laptop), so my first task was to turn on the backlight. I referred to the pinout of the connector, and the schematics of the laptop main board to try to figure out how it was being controlled.

The next blog post LCD panel + FPGA with an HDMI sink = External Display will continue from here: implement a HDMI sink, and display the received video on the LCD panel.

Not long ago, we published some articles about controlling different kinds of displays, using your FPGA. On a VGA screen, on a small LCD screen, on a PSP LCD or even for the old, but nasty-analog-signaled NTSC system.

And today, we share with you another great tutorial on how to control a LCD TFT, that takes advantage of the ability of a FPGA to fully control what happens on every single clock cycle.

You may think, well, another LCD tutorial, more on the same…And you will be wrong. There are no identical systems. Each one has its own features which make it unique, and we want you to know them.

This is a very well explained tutorial that gives you all the files you will need to successfully implement it: schematics, VHDL code files, Project files, datasheets of the display…Everything!

In addition the author takes some extra time to explain what really matters about this project and what makes it different from any other “How to control your LCD screen with your FPGA”. To properly control a TFT display you need two specific timed signals: DCLK (Pixel Clock) and DE (Data Enable). Why the code lines that control these two signal are coded the way they are is carefully explained in the article so you don´t want to miss it. Understanding this will make you capable of playing with any other TFT screen you may find.

Abstract: laptop lcd display interface 20 pin laptop lcd connector 7 inch 800x480 LCD panel 14" laptop lcd pin configuration 14 laptop lcd pin configuration lcd monitor display block diagram graphic lcd panel fpga example laptop lcd 20 pin diagram toshiba LCD 320X240

Text: Objective The DVI Input to LCD reference design setup (Figure 1) demonstrates an IGLOO® FPGA as an LCD , necessary LCD data to the panel (RGB and control signals). It receives data from the Digital Video Interface , inside the FPGA takes care of the source image storage and pulling out images from the SDRAM for LCD , NVIDA graphic chip, the following instructions apply. 1. In Windows, select Control Panel > Display , Reference Design 3. In this window, there is a tab for the NVIDIA graphic card control panel . In Figure 5

Abstract: fpga TFT altera block diagram of Video graphic array Judd Wire Cyclone TFT bt.656 to RGB GRAPHICAL LCD DIAGRAM bt.656 to RGB LCD display FPGA-based LCD driver circuit E144

Text: infotainment designs. Through a simple UART, the FPGA becomes the graphic display controller for the system. It , example , a communication protocol typically used to address a VF or character-based LCD could easily be , Creating Low-Cost Intelligent Display Modules With an FPGA and Embedded Processor The LCD controller design within the FPGA easily adapts to a variety of standard and custom LCD resolutions (see Figure 4). , intrinsic benefit of the LCD controller within the FPGA is that it can be customized or adapted to create

Text: LCD , and other panel displays such as EL and Plasma) SlixBITBLK Bit Block - 2D Graphic , . Graphic Display Panel On-chip Analog Channels External Processor Core SlixMEM Applications , their designs to multiple FPGA devices. Solution Comparisons There are several popular display/ LCD , "s SD1000 is another similar example of an ASSP solution for display/ LCD control. One of the major issues , supported on many leading LCD panel technologies and vendors. However, the key difference is that this

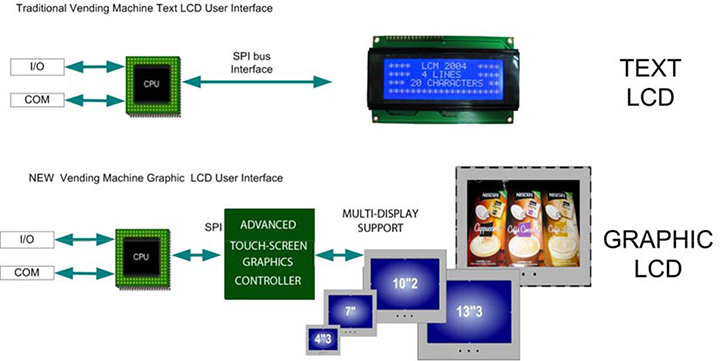

Abstract: 7 inch TFT LCD Wvga touchscreen 8051 vending machine vending machine using microcontroller how vending machine work simple vending machine 8051 lcd qvga 320x240 block diagram vending machine using FPGA lcd qvga 320x240 fpga 8051 for vending machine

Text: . Refrigerators have begun to appear with large graphic LCD screens offering features once considered esoteric , many different LCD Panels Scalable graphic resolution from QVGA(320x240) up to UXGA (1600x1200, the LatticeECP2 FPGA family. The LCD-Pro implements a powerful, fully configurable 16bpp LCD video , console-mounted LCD panels with touch-screen capability. Building Automation HMI comprises touch-screen , marine camera equipment. Household appliances like washers now sport color touch-screen graphic

Abstract: graphic lcd panel fpga example 800x480 resolution GRAPHICAL LCD DIAGRAM bt.656 to RGB LCD display bt.656 parallel to RGB 565 block diagram of Video graphic array development trends in car manufacture LCD based on I2C lcd double lamp CCFL

Text: nature of FPGAs supports a variety of LCD panel requirements. For example , many different memory , FPGA and soft-core embedded processor technology, the first LCD panel driver architecture that , , designers can quickly and efficiently assemble the elements needed to drive a wide range of LCD panel configurations for implementation within an FPGA . Altera provides an LCD driver architecture that, for the first , the necessary throughput and video bandwidth to drive a two-way viewing LCD panel with 800x480

Abstract: REMOTE CONTROL bill of material embedded c programming examples CYCLONE III EP3C25F324 FPGA CYCLONE 3 ep3c25f324* FPGA video card schematic tv SCHEMATIC graphics card SCHEMATIC USB to VGA hmi application note graphic lcd panel fpga example

Text: systems targeting the low - cost, low - power Cyclone III FPGA can be evaluated by simply using the LCD color touch panel to scroll through and load your demo of choice. These processor systems showcase the unique benefits of FPGA - based processors such as reducing bill of material (BOM) costs by integrating powerful graphics engines within the FPGA , reducing operating costs by upgrading your system over , Edition is composed of the daughtercard and features: ? Cyclone III FPGA Starter Kit and an LCD /VGA

Abstract: fpga TFT LCD display Human Machine Interface vending machine design using microcontroller vending machine graphic lcd panel fpga example vending implementation for vending machine LVDS display tcon QVGA GRAPHICS LCD DISPLAY TFT LCD display Human Machine Interface

Text: the FPGA , communicates with a host system or processor for control tasks, and with a touch-screen LCD , freestanding vending machines for hot beverages. The manufacturer needed an innovative new graphic LCD touch , Semiconductor White Paper Embedded LCD Control Applications Requirements Graphical LCD displays are , advanced LCD graphics solutions in their designs in order to support multiple display and processor types , opportunity. Following are some of the important general requirements for embedded LCD control applications

Text: generation of 1280x1024 flat panel monitors are examples of just such products. The monitors are unique in that they offer very high graphic performance with some very special features. They are built using an active matrix LCD screen with a resolution up to 1280x1024, and are driven via a ten-foot cable from a SiliconGraphics IndyTM or Indigo2TM workstation. The back lighting of the flat panel display is removable so that it can be placed on an overhead projector and used as a projection panel . With these features, we

Abstract: 7 inch 800x480 LCD panel touch lcd digital 7 inch TFT LCD WVGA QVGA GRAPHICS LCD DISPLAY rgb led video colour display ITU656 M25P32 BLOCK DIAGRAM OF 4 wire resistive TOUCH panel implementation of eeprom interfacing with i2c

Text: Controller UltiEVC Video Controller Touch Dimming TTL RGB LCD Panel Touch Screen UltiEBB , Video Input Ports LatticeECP2-based FPGA Module 7" WVGA LCD Color Touch Display LCD-Pro , LatticeECP2TM low-cost FPGA family. The library contains several IP cores that provide advanced graphics system functionality. Kit Includes 7" LCD Color Touch Display, Video Camera, Eval Board, & more , Integrates LCD Display Support from 2 inches to 23 inches and larger Easy to add Custom or Proprietary IP

Abstract: graphic LCD screen BLOCK DIAGRAM OF 4 wire resistive TOUCH screen lcd color cvbs video frame grabber bt.656 to RGB LCD display spi controller with apb interface Flat Panel Display Controller ITU656 M25P32

Text: Controller UltiEVC Video Controller Touch Dimming TTL RGB LCD Panel Touch Screen UltiEBB , Video Input Ports LatticeECP2-based FPGA Module 7" WVGA LCD Color Touch Display LCD-Pro , LatticeECP2TM low-cost FPGA family. The library contains several IP cores that provide advanced graphics system functionality. Kit Includes 7" LCD Color Touch Display, Video Camera, Eval Board, & more , Integrates LCD Display Support from 2 inches to 23 inches and larger Easy to add Custom or Proprietary IP

Abstract: transistor 34N nx smv r010 schematic diagram lcd monitor samsung 370HR net eN8 schematic diagram lcd monitor advance 17 DISPLAYTECH ML550 SMV-R005-1.0 5 mOhm

Text: 2.5V. The FPGA is connected to the graphic LCD display through a set of voltage-level converting , . . . . . . . . . . . . . . . . . . . . Controller LCD Panel Connections . . . . . . . . . . . . , . . . . . . . . . . . . . . . . . . . . . . . . . LCD Panel Used in Full Graphics Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . LCD Panel Used in Character Mode . . , Figure 1-1 shows the ML550 Development Board. JTAG Connector Graphic 64 x 128 LCD XCONFIG

Text: 1280x1024 flat panel monitors are examples of just such products. The monitors are unique in that they offer very high graphic performance with some very special features. They are built using an active matrix LCD screen with a resolution up to 1280x1024, and are driven via a ten-foot cable from a Silicon Graphics IndyTM or Indigo2TM workstation. The back lighting of the flat panel display is removable so that it can be placed on an overhead projector and used as a projection panel . With these features, we

Text: devices. Low power design based on Flash FPGA architecture. Intelligent Display Control with Video System Graphic Display Panel Ext. Video Decoder Applications · · · · · Automated , Blocks SlixCDC Compact Display Controller (supports STN, DSTN, TFT LCD , and other panel displays , Configurable display controller supports different kinds of LCD , EL, Plasma display panels. Various display , display control solution is available for implementation on Actel"s Fusion, a Flash based FPGA

Abstract: DISPLAYTECH* 64128 XC4VLX25-FF668 AA15 Fairchild XC4VLX25 Xilinx lcd display controller design xc4vlx25ff668 ML461 VC4VLX25 graphic lcd panel fpga example

Text: Controller LCD Panel Connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . , . . . . . . . 100 LCD Panel Used in Full Graphics Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 100 LCD Panel Used in Character Mode . . . . . . . . . . . . . . . . . , . External Interfaces: System ACE Controller, ML410 Z-DOK+, LCD HSTL 36 36 FPGA #4 LX25/ FF668, #4 device. FPGA #4 also implements some of the auxiliary functions, such as connections to the LCD

Abstract: vhdl code for lcd display LCD module in VHDL 3D LCD controller UART using VHDL vhdl code for game vhdl code for sdram controller 3D Accelerator fpga TFT altera processor control unit vhdl code

Text: create and use to connect blocks in the FPGA . For example , with just a few mouse clicks in SOPC Builder , -D graphic operations because they require a lot of arithmetic operations and most mobile device processors , reduce the computing time. In this project, we developed a 3-D graphic display system that quickly computes 3-D graphic operations by including a hardware 3-D accelerator in the chip, and creating applications in it. Using the Nios® II processor to develop 3-D graphic displaying system makes it possible to

Abstract: 128X64 graphical LCD display specifications 128X64 graphical LCD EP3C120F780C7N 128X64 graphical LCD screen rohs 128X64 graphical LeD screen AC12 AH15 cycloneIII DDR2 chip

Text: . . . . . . . . . . . . . . . . . . 68 The Graphic LCD Tab . . . . . . . . . . . . . . . . . . . . , The Cyclone III FPGA Development Kit ships with the Board Update Portal design example stored in the , switch (SW5) in position 0, the Cyclone III FPGA configures with the Board Update Portal design example , memory DDR2 memory Graphic LCD The application allows you to exercise most of the board , Graphic LCD Tab The Graphic LCD tab allows you to write to the LCD on your board. Figure 63 shows the

Text: VCC LCD Panel Pin Description Data Signal Graphic Display Data Blue-data Data Signal Graphic , -55343GD035JU-LW to the S1D13513 The following diagram shows an example implementation of the T-55343GD035JU-LW panel , -55343GD035JU-LW to the S1D13513 LCD Panel Connector Pin# 1 LCD Panel Pin Name RL 2 3 4 5 6 7 , DB4 29 DB3 30 4 TB DB2 LCD Panel Pin Description Input to select Source driver , -55343GD035JU-LW LCD Panel Connector Pin# LCD Panel Pin Name LCD Panel Pin Description 31 DB1 32

Abstract: hp LCD inverter SCHEMATIC 16*2 lcd module theory LCD 240x128 interfacing and programming 240x128 graphics lcd lcd data image 240*128 interfacing of a 16*2 lcd display LC7942 block diagram images of lcd display 16x2 CFAG240128D-FMI-T

Text: Substrate Panel The graphics display panel substrate defines the resolution of the LCD . For example , a , Value(s) None Example ZDrawlines(); AN0196021207 Page 19 of 30 Interfacing a Graphic LCD , Interfacing a Graphic LCD with a Z8 Encore! XP® 64K Series Flash MCU ZCleargraf Synopsis Clears LCD panel , Example ZCleargraf(); AN0196021207 Page 25 of 30 Interfacing a Graphic LCD with a Z8 Encore , Application Note Interfacing a Graphic LCD with a Z8 Encore! XP® 64K Series Flash MCU AN019602

Abstract: LM64C35 Xilinx lcd display controller TFT LCD display Human Machine Interface schematic LJ64H034 VHDL code for dac 128X64* control LMG9520 sharp lcd panel pinout LQ121s1dg11

Text: double panel displays · Gray and color shades using XcolorsTM; up to 4 gray levels or 256 colors , external register Supports Electroluminescent, Plasma, LCD and CRT displays Support for two video pages , graphic accelerator - Automatic blink/highlight/inverse function - Huffman - RLE BMP decompressor , , CTRL. General Description The logiCVC Compact Video Controller is a graphic video controller , unit and character generator, can be easily supplemented. The logiCVC controls flat panel displays

Text: . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Controller LCD Panel Connections . , . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . LCD Panel Used in Full Graphics Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . LCD Panel Used in Character , : System ACE Controller, USB, RS-232, LCD SSTL18/SSTL2 SSTL18 FPGA #2 XC5VLX50T/ FFG1136 FPGA #3 , Virtex-5 FPGA ML561 Memory Interfaces Development Board User Guide UG199(v1.2.1) June 15

Text: Character Character Type Type Graphic Graphic Type Type COF UNIT WITH LCD EXAMPLE 3 Boca Raton , 2 mm away from chip. 3. ACF: Anistropic, Conductive Film COF UNIT WITH LCD EXAMPLE 1 Chip on Flex LCD Custom Module COF UNIT WITH LCD EXAMPLE 2 2 PRODUCT INFORMATION SHARP COF , Keypads LCD Touch Panel Touch Panel MPU MPU Peripherals Peripherals Touch Panel Touch Panel Character Character Type Type Camas, WA Ph (360) 834-2500 Fax (360) 834-8903 Graphic

Abstract: 24 pin tft lcd pinout details MK70F15 12BPP 43WQW3T-4 3" wqvga 37 pin LCD pinout TWR-K70F120M schematic Smart lcd power supply unit Hsync Vsync crt tv TWRK70F120M

Text: register determines the starting position of the graphic window on the LCD panel . // set LCD graphic window , recommended to select an LCD panel which works most of the time in its native orientation to avoid extra image , (RGB444) · 16bpp(RGB565) · 18bpp(RGB666) · 24bpp(RGB888) 2.2 LCD types · Synchronous panel (Dumb , . This value is equal to the Vertical Resolution of the LCD . Using the same WVGA (800x480), as an example , Business Information Kinetis LCD controller Figure 6. Vertical timing example VSYNC period involves

Text: 1.0 Two Layers Character/ Graphic LCD Controller For example : show letters ABCDE at coordinate(0 , / Graphic LCD Controller 3. Touch Panel Mode 3-1 How to Use RA8806 Embedded Touch Panel Controller ? , RAiO RA8806 Two Layers Character/ Graphic LCD Controller FAQ Preliminary Version 1.0 June , www.raio.com.tw RA8806 Preliminary Version 1.0 Two Layers Character/ Graphic LCD Controller Update , / Graphic LCD Controller Contents Page 1. General Functions

Abstract: CYCLONE III EP3C25F324 FPGA SD host controller vhdl graphic lcd panel fpga example CYCLONE 3 ep3c25f324* FPGA EP3C25F324 INTEL 8751 vhdl code for a 16*2 lcd SD Card and MMC Reader Micrium

Text: demonstrations stored on an SD Card using the LCD touch panel . An application consists of a FPGA hardware image , Embedded Evaluation Kit, Cyclone® III Edition includes a full-featured FPGA development board, LCD , LCD Color Touch Panel to scroll through and load your demonstration of choice. These processor , loaded using the application selector on your LCD touch panel . These demonstrations are implementations , FPGA Starter Board DDR SDRAM LCD Multimedia Daughtercard Cyclone III FPGA SSRAM Nios II

Text: RA8806 Preliminary Version 1.0 Two Layers Character/ Graphic LCD Controller REG [C3h] Touch Panel , RAiO RA8806 Two Layers Character/ Graphic LCD Controller Specification Preliminary Version 1.0 , /174 www.raio.com.tw RA8806 Preliminary Version 1.0 Two Layers Character/ Graphic LCD , . 4. Two Layers Character/ Graphic LCD Controller Content Page General Description , Layers Character/ Graphic LCD Controller 6-8 Interrupt and Busy

Microchip"s LCD PIC microcontroller family is a Flash-based, power managed family of LCD-enabled microcontrollers. Microchips LCD PIC microcontroller family meets low power design requirements including driving the LCD display in sleep mode while maintaining desired functional features. With the ability to select from an array of available LCD PIC microcontrollers, a designer can provide additional value by creating scalable designs and products. This gives the designer flexibility to offer different solutions based on the demand of varying market segments all from a single design.

The VGA image signal generator that the purpose of this invention is to provide a kind of FPGA, it can be able to realize various numerals, literal, colour bar, the output of ROM picture signal.The system handles of its image display controller is consuming time less than 20ms, has reached real-time requirement (50/second) fully.Can be used as the display apparatus test signal generator, be applicable to display factory or maintenance personal, computer house and user of unit even personal user, need not to connect picture demonstration, test, the inspection of main frame, with the maintenance post debugging, by observation and analysis, can judge the overall performance or the maintenance back effect of display to test pattern.

In order to solve the existing problem of background technology, the present invention is by the following technical solutions: it is made up of LCD display 1, singlechip controller 2,4X4 rectangle keyboard 3, power supply 4, FPGA5, clock circuit 6, interface circuit 7, VGA display 8; LCD display 1 is connected with singlechip controller 2, and singlechip controller 2 is connected with 4X4 rectangle keyboard 3, and singlechip controller 2 is connected with FPGA5, power supply 4 is connected with FPGA5, clock circuit 6 is connected with FPGA5, and FPGA5 is connected with interface circuit 7, and interface circuit 7 is connected with VGA display 8.

Principle of work: FPGA is the core of total system, by it is programmed exportable RGB tristimulus signals and HS, VS row-field scanning synchronizing signal.Accept the control signal of single-chip microcomputer output as FPGA after, inner data selector module is according to the corresponding image generation module of control signal gating, output image signal, send into the VGA display with the row-field scanning clock signal by 15 pin D type interface circuits, on the VGA display, just can see corresponding coloured image.The required work clock of FPGA is provided by the active crystal oscillator of outside high precision; Singlechip controller is analyzed the keyboard scan result, and the control LCD MODULE shows function corresponding, shows output image and button control model by LCD, and sends corresponding control signal and give FPGA,

The present invention has following beneficial effect: can be able to realize various numerals, literal, colour bar, the output of ROM picture signal.The system handles of its image display controller is consuming time less than 20ms, has reached real-time requirement (50/second) fully.Can be used as the display apparatus test signal generator, be applicable to display factory or maintenance personal, computer house and user of unit even personal user, need not to connect picture demonstration, test, the inspection of main frame, with the maintenance post debugging, by observation and analysis, can judge the overall performance or the maintenance back effect of display to test pattern.

Ms.Josey

Ms.Josey

Ms.Josey

Ms.Josey