tft lcd controller vhdl factory

Not long ago, we published some articles about controlling different kinds of displays, using your FPGA. On a VGA screen, on a small LCD screen, on a PSP LCD or even for the old, but nasty-analog-signaled NTSC system.

And today, we share with you another great tutorial on how to control a LCD TFT, that takes advantage of the ability of a FPGA to fully control what happens on every single clock cycle.

You may think, well, another LCD tutorial, more on the same…And you will be wrong. There are no identical systems. Each one has its own features which make it unique, and we want you to know them.

This is a very well explained tutorial that gives you all the files you will need to successfully implement it: schematics, VHDL code files, Project files, datasheets of the display…Everything!

In addition the author takes some extra time to explain what really matters about this project and what makes it different from any other “How to control your LCD screen with your FPGA”. To properly control a TFT display you need two specific timed signals: DCLK (Pixel Clock) and DE (Data Enable). Why the code lines that control these two signal are coded the way they are is carefully explained in the article so you don´t want to miss it. Understanding this will make you capable of playing with any other TFT screen you may find.

Digital Blocks TFT LCD Controller reference design enables you to accelerate the design-in of TFT LCD panel displays in your system. The reference design centers on the Digital Blocks DB9000AVLN TFT LCD Controller intellectual property (IP) core, which is available in netlist or VHDL/Verilog HDL register transfer level (RTL) formats.

The DB9000AVLN core contains an Avalon® Memory-Mapped system interconnect for interfacing to the Nios® II embedded processor and SDRAM or SRAM controllers (either memory can serve as the frame buffer). Software supplied with this reference design runs on the Nios II embedded processor to place an image in the frame buffer memory and invokes the DB9000AVLN core to drive the LCD panel.

Using the Intel® Quartus® Design Software, you can instantiate the TFT LCD Controller reference design in a Cyclone®, Cyclone® II, or Cyclone® III FPGA development kit. See the Demonstrated Intel® Technology section for a complete list of supported Intel® FPGA development kits.

You can connect your LCD panel to the Intel FPGA development kit with the fabrication of an appropriate cable. Please contact Digital Blocks for more details.

TFT-LCD technology is based on semiconductor IC manufacturing processes, and is unique in that it uses glass substrates rather than traditional silicon wafers. For the TFT manufacturing process, thin film formation, such as CVD and PVD processes, is a very important part. The ODF process has been developed for the assembly of color filters and TFT substrates, and is used in large size LCDs.

First of all, the movement and arrangement of liquid crystal molecules need electrons to drive, so in the carrier of liquid crystal – TFT glass, there must be able to conduct the part to control the movement of liquid crystal, here will use ITO (Indium TIn Oxide, transparent conductive metal) to do this thing. ITO is transparent, also known as thin film conductive crystal so that it will not block the backlight.

The different arrangement of liquid crystal molecules and the rapid movement changes to ensure that each pixel accurately display the corresponding color, and the image changes precisely and quickly, which requires precision control of the liquid crystal molecules. ITO film requires special processing, as if printed circuitry on a PCB board, drawing conductive lines throughout the LCD board.

For array panels with back-channel etched TFT structure.The main process can be divided into 5 steps (5 lightings) according to the sequence of the layers to be made and the interrelationship between the layers.

The process includes: PECVD triple layer continuous film formation, island lithography, island dry lithography and other processes. After these processes, the final amorphous silicon island for TFT is formed on the glass substrate. The graphics obtained after the process is completed are shown in the following figure.

Specific processes include: S/D metal layer sputtering into a film, S/D lithography, S/D wet lithography, channel dry lithography and other processes. After these processes, the source, drain, channel and data lines of the TFT are finally formed on the glass substrate. At this point, the TFT has been produced. The graphics obtained after the process is completed are shown in the following figure.

The process includes PECVD, photolithography, and dry lithography of vias. After these processes, the final TFT channel protective insulation layer and guide through the hole are formed on the glass substrate. The graphics obtained after the process is completed are shown in the following figure.

Color filters can be produced by various methods; photolithography is a typical method. In photolithography, color filters are produced by exposing a glass substrate coated with a photographic color resist through a photomask. The resist is hardened to form the RGB pattern of the LCD.

When making LCD panels it is impossible to produce them one by one, which is too inefficient, so multiple pieces are processed at once and separated by cutting.

In between of these you will see a small green connector board, which is our own 7-inch LCD Breakout board with the required switch-mode power supply for powering the LED backlight, together with the interface connector with the 18-bit color signals, Pixel Clock, Data Enable and PWM.

Where the TDEH and TDE are definitions as found in the datasheet. In the top of our VHDL code all these timing definitions has been programmed as constants:

Text: Digital Blocks DB9000AVLN Semiconductor IP Avalon Bus TFT LCD Controller General Description The Digital Blocks DB9000AVLN TFT LCD Controller IP Core interfaces a microprocessor and frame , or SDRAM. Figure 1 depicts the system view of the DB9000AVLN TFT LCD Controller IP Core embedded within a FPGA. FPGA Avalon-MM System DB9000AVLN TFT LCD Controller Processor TFT LCD Panel , On-Chip Memory SRAM Memory Chip SDRAM Memory Chip Figure 1: DB9000AVLN TFT LCD Controller

Abstract: vhdl code for lcd display LCD module in VHDL 3D LCD controller UART using VHDL vhdl code for game vhdl code for sdram controller 3D Accelerator fpga TFT altera processor control unit vhdl code

Text: address of the frame buffer, which is placed in SDRAM. The thin-film transistor ( TFT ) LCD controller , Controller SDRAM Controller Avalon Bus 2 TFT LCD Controller TFT LCD Avalon Bus 4 SDRAM , LCD Controller first and displayed a sample image to the TFT LCD with a simple software program. Next , . We developed the LCD Controller module in VHDL , created a Symbol File of it, and connected it to the , association in the Quartus® II software. We created each block in the LCD Controller module using VHDL , and

Abstract: DB9000 LCD 640X200 240x320 TFT LCD display circuit diagram TFT circuit diagram 16bit rgb lcd interface 240x320 rgb lcd 7" 18-bit digital LCD controller 240x320

Text: Digital Blocks DB9000OCP Semiconductor IP OCP Interface TFT LCD Controller General Description The Digital Blocks DB9000OCP TFT LCD Controller IP Core interfaces a microprocessor and frame , DB9000OCP TFT LCD Controller IP Core embedded within an integrated circuit device. ASIC, ASSP Device DB9000OCP TFT LCD Controller Processor OCP Slave Port TFT LCD Panel OCP Master Port OCP 2.2 , Memory Chip Figure 1: DB9000OCP TFT LCD Controller System Diagram Features Wide range of

Abstract: sharp 640x240 lcd amba ahb master sram controller AMBA AHB memory controller sharp lcd panel 20 pin AMBA AHB DMA 640x200 sharp pixel vhdl 320x240 VHDL LCD 640X200

Text: Digital Blocks DB9000AHB Semiconductor IP AHB Bus TFT LCD Controller General Description The Digital Blocks DB9000AHB TFT LCD Controller IP Core interfaces a microprocessor and frame , or SDRAM. Figure 1 depicts the system view of the DB9000AHB TFT LCD Controller IP Core embedded within an integrated circuit device. FPGA, ASIC, ASSP Device DB9000AHB TFT LCD Controller Processor AHB Slave Port TFT LCD Panel AHB Master Port AMBA 2.0 AHB Bus SDRAM Controller

Abstract: VHDL code for ADC and DAC SPI with FPGA usb 2.0 implementation using verilog Xilinx Ethernet development nanoboard vhdl code for i2c XC3S1500 SPARTAN-3 BOARD SPARTAN 6 Configuration SPARTAN 6 peripherals datasheet XILINX SPARTAN XC3S1500

Text: board specifications · Integrated color TFT LCD panel (320x240) with touch screen that facilitates , · FPGA design entry in C, OpenBus, Schematic, VHDL and Verilog · Supports range of swappable , , mixer, line in/out and stereo speakers · VHDL simulation engine, integrated debugger and waveform , and alternate technology options. · Onboard memory accessible by NanoTalk Controller 256K x 32 , -3 Daughter Board (DB30) · Home/Reset button Home button enables firmware to take control of TFT panel

Abstract: VHDL code of lcd display 7 segment display 5611 Xilinx lcd display controller video pattern generator vhdl ntsc VHDL code for interfacing renesas with LCD bitblt raster PAL to ITU-R BT.601/656 Decoder Xilinx lcd display controller design fpga frame buffer vhdl examples

Text: supported on request. Display Controller The display controller handles the interface to the LCD / TFT , and the LCD / TFT displays. BADGE includes a number of GPUs (Graphics Processing Units). See fig 1 , , Technical Notes Design File Formats BitSim AB EDIF netlist, VHDL Constraints Files S:t , URL: www.bitsim.com .ucf Verification VHDL Test Bench, Command files Instantiation Templates VHDL Reference Designs & BADGER-Ref Design, Application Notes API, Decompression

Abstract: Verilog code for ADC and DAC SPI with FPGA vhdl code for rs232 receiver using fpga nanoboard 3000 240x320 Color LCD schematic motherboard coil EP3C40F780C8N nanoboard XC3S1400AN-4FGG676C VHDL code for PWM

Text: Integrated color TFT LCD panel (240x320) with touch screen that facilitates dynamic application interaction , 8Mbit SPI flash memory devices one containing Primary boot image for Host Controller , one containing golden boot image for Host Controller , two for use by user FPGA (for boot/embedded purposes) · SPI , high-capacity FPGAs · Host (NanoTalk) Controller hosts the NanoBoard firmware. Responsibilities include , handled by an ISP1760 Hi-Speed USB Host Controller · SVGA interface (24-bit, 80MHz) · Variety of

Abstract: LM64C35 Xilinx lcd display controller TFT LCD display Human Machine Interface schematic LJ64H034 VHDL code for dac 128X64* control LMG9520 sharp lcd panel pinout LQ121s1dg11

Text: , e.g., various LCD technologies (TNM, STNM, TFT , analogous RGB TFT ), electroluminescent displays and , logiCVC Compact Video Controller May 4, 2001 Product Specification AllianceCORETM Facts , external register Supports Electroluminescent, Plasma, LCD and CRT displays Support for two video pages , LogiCVC.ucf Verification Viewlogic.cmd files Instantiation Templates VHDL , Verilog Reference Designs and , . Assuming all core I/Os are routed off-chip May 4, 2001 1 logiCVC Compact Video Controller 9

Abstract: CMOS sensor 2 megapixel 1600 x 1200 pixels K2607 transistor XAPP390 ALPHANUMERIC DISPLAY image ccd image sensor CMOS image sensor PAL Micron 0343 optrex lcd VGA RGB LCD control

Text: well as reflect light from the front of the LCD . Most TFT LCDs have integrated IC drivers that , signal. Blue image data signal. The Optrex LCD TFT is compatible with four types of VGA timing. The , is available for download in " VHDL Code," page 18. Introduction Digital cameras have become , Gamma Control: Corrects the image for observation on an LCD . · Sharpening Control · , :0] B[4:0] X390_04_090203 Figure 4: Video Capture Timing LCD Technology In a digital camera

Text: . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65 Chapter 8: PLB TFT LCD Controller , Chapter 8: PLB TFT LCD Controller Figure 8-1: High-Level Block Diagram. . . . . . . . . . . . . . . . . . , Controller " · Chapter 7, "OPB PS/2 Controller (Dual)" · Chapter 8, "PLB TFT LCD Controller , MicroBlaze INT ILMB IPIF IPIF IPIF IPIF TFT LCD Controller DDR MEMC DDR Memory MDM PS , (if enabled) · VGA TFT LCD Controller The DCR specification requires that the DCR master and

Abstract: 10.1 inch lcd with led backlight 40 pin connector pinout vhdl code for rs232 receiver philips lcd 15.4 pinout PL041 vhdl code for a 16*2 lcd schematic diagram tv sharp LM-XCV2000 schematic diagram lcd tv sharp inverter 9PIN MMC socket

Text: Sharp 8.4" TFT (J14) LCD and touchscreen (J27) EXPA Socket Buffer Touchscreen controller , Reference Manual (ARM DDI 0187) · ARM PrimeCell Color LCD Controller (PL110) Technical Reference Manual , outputs for a: · VGA or SVGA monitor connected to J30 · Sharp LQ084V1DG21 8.4 inch TFT VGA LCD panel , . Touchscreen controller , ) · ARM PrimeCell Vectored Interrupt Controller (PL190) Technical Reference Manual (ARM DDI 0181) ·

Text: size. Dimensions refer to package body size. Memory Controller Memory Microphone User Interface & TFT Controller Touchscreen Keypad CPU Bus Interface HCI Bridge LCD CPU Power , ispMACH 4000Z ispMACH 4000Z vs. the Competition PWM/Buzzer RS232 LCD Controller Power , Controller Memory Controller Video Out 1394 LCD Controller System Control MPEG2 , amplifier · set top box · home gateway · home theater · digital camcorder · LCD TVs · digital projectors ·

Text: * series . 22 LCD controller LCD controller with Camera I/F Video Encoders Bridge Devices Organic EL controller VFD Controller LCD controller for automotive EPD controller , display External bus S1C17500 series 15 LCD controller External bus S1C17800 series 16 EPD Driver S1C17F00 series 16 LCD controller S1C17Family(Low Power) 10 Serial I/O , types of sensors and the EPD Driver/ controller , LCD driver/ controller that covers the wide display

Abstract: LCD module in VHDL LFXP2-5E-5TN144C lcd module verilog "1 wire slave interface" verilog wishbone vhdl for lcd lfxp25e5tn144c Driver/S6A0069 LCMXO2280C-3T100C

Text: WISHBONE-Compatible LCD Controller November 2010 Reference Design RD1053 Introduction , This design is used to control dot matrix LCD modules that have an on-board controller and driver. The , LCD Module Interface wb_stb_i lcd_db[7:0] lcd_r5 lcd_rw LCD Module with Controller and , _01.2 WISHBONE-Compatible LCD Controller Lattice Semiconductor Signal Descriptions Table 1. Signal Descriptions , WISHBONE-Compatible LCD Controller Lattice Semiconductor the input signal lcd_done is active, indicating that

Text: . 22 LCD controller . 22 S1D13* series LCD controller with Camera I/F , . 23 S1D13* series LCD controller for automotive , display External bus S1C17500 series 15 LCD controller External bus S1C17800 series 16 LCD controller 16-bit S1C88Family Font ROM For high resolution display Small package

Text: External bus S1C17500 series 14 LCD controller External bus S1C17800 series 15 EPD Driver S1C17F10/F50 series 15 LCD controller S1C17Family(Low Power) 10 For low-power , / controller , LCD driver/ controller that covers the wide display area into a single chip design. They can , . 08 MCUs Micro Controller Unit 2-1 4-bit Microcontrollers , , S2D13* series . 22 â LCD controller â LCD controller with Camera I/F

Text: website. Touchscreen TFT Display A 4.3â wide-format vivid color LED backlit LCD screen is used on , -mbps Ethernet, HDMI Video, 128MB DDR2 memory, 4.3â LED backlit LCD touchscreen, 128x32 pixel OLED display , port 4.3â wide-format vivid color LED backlit LCD screen 128x32 pixel 0.9ââ WiseChip/Univision , respective owners. Anvyl Reference Manual files from VHDL , Verilog, or schematic-based source files , . The following devices are present on each rail: ⢠5V : USB-HID connectors, TFT touchscreen

Text: . 30 LCD controller . 30 S1D13* series LCD controller with Camera I/F , . 31 S1D13* series LCD controller for automotive , No display External bus S1C17500 series 18 LCD controller External bus S1C17 Family 12 Small package S1C17 Family S1C63500 series S1C17800 series 19 LCD controller

Text: Error Detection Video Frame Buffer Dual Display Controller Graphics LCD Controller LCD Controller , Interface Controller RD1095 LCD Controller RD1053 P P LED/OLED Driver RD1103 P P , I2C Master Controller RD1005 VHDL I2C Slave/Peripheral RD1054 VHDL I2C Slave to SPI , ) RD1100 VHDL PWM Fan Controller RD1060 VHDL SPI GPIO Expander RD1073 VHDL Serial , Controller DC-DC Secondary DC-DC Primary Fan Control DC-DC Secondary Payload ICs

Text: /13800 series 3-2 LCD Controllers 60 62 ILCD controller-drivers for small-sized displays , series ILCD drivers for grayscale displays S1D18000 series,S1D17900 series ,S1D19000 series 2 LCD , 70 IIEEE1394 controller S1R72000 series IUSB2.0 device controller S1R72000 series ISCSl controller S1R72100 series 3-5 Power Supply ICs IPower supply ICs for logic S1F70000 series IPower , number New number SED4100 S1D41000 SED4101 S1D41010 SED4180 S1D41800 IEEE1394 controller

Abstract: led sign board circuit diagram SD178A VHDL code of lcd display vhdl code SD178 led sign diagram sign board LED DISPLAY CIRCUIT diagram EP2C20F484C7 Altera DE1 Board Using Cyclone II FPGA Circuit

Text: voice circuit and an nRF2401 RF module on the DE1 board Design a SD178A controller using VHDL , following tasks: Designed the SD178A controller using VHDL Compiled the SD178A sub-drivers using , and an nRF2401 RF module on the DE1 board Design a SD178A controller using VHDL Compile , bus station sign using a 320 x 240 LCD Locate the bus correctly by touching the touch screen , _1_debug LCD_pio JTAG-UART * Extensive Circuit Nios II Processor EP2C20F484C7 320 x 240 LCD Touch

Text: LCD Controller RD1053 P P LED/OLED Driver RD1103 P P LPC (Low Pin Count) Bus , I2C Master Controller RD1005 VHDL I2C Slave/Peripheral RD1054 VHDL I C Slave to SPI , ) RD1100 VHDL PWM Fan Controller RD1060 VHDL SPI GPIO Expander RD1073 VHDL Serial , Controller DC-DC Secondary DC-DC Primary Fan Control DC-DC Secondary Payload ICs , +12 / 24V Hot swap Controller P P P P P P Low Voltage Positive Supply Hot-Swap

Abstract: ch7301 DVI VHDL DVI VHDL xilinx ch7301 CHRONTEL 7301 Xilinx XPS Thin Film Transistor(TFT) Controller TFT controller XC4VLX25-FF668-10 a/ch7301 DVI VHDL DS695

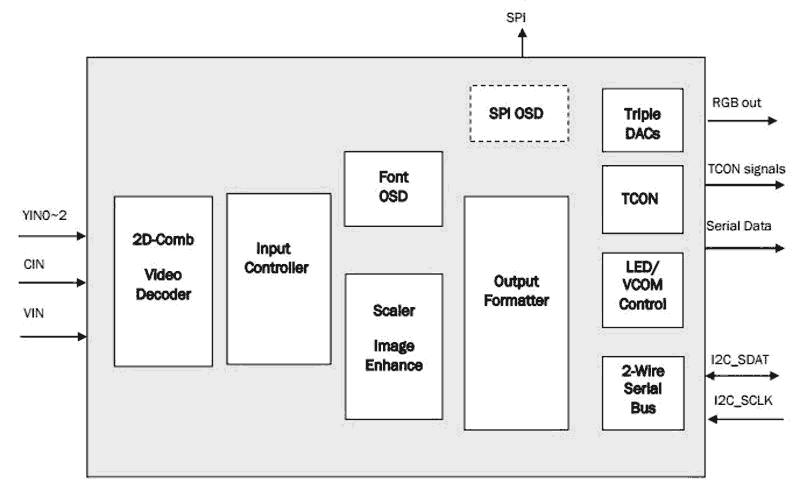

Text: 0 XPS Thin Film Transistor ( TFT ) Controller (v2.00a) DS695 September 16, 2009 Product Specification 0 0 Introduction LogiCORETM Facts The XPS Thin Film Transistor ( TFT ) controller is a hardware display controller IP core capable of displaying 256k colors. The XPS TFT controller connects as , Film Transistor ( TFT ) Controller (v2.00a) Functional Description The XPS TFT controller is a , chip when the DVI interface is selected. The XPS TFT controller block diagram is shown in Figure 1

Abstract: S1D15712 Mini USB 5Pin F SMT S1D15721 stepping motor EPSON 323 speed control of SMALL dc motor using dtmf LED Dot Matrix vhdl code vhdl code 16 bit processor S1D15E00D01B S1D15716

Text: . 30 TFT LCD Drivers for mobile , Mini LVDS Transmitter ARM7TDMI UART LCD Controller ARM720T 10/100/1000base Ethernet MAC , 8-bit FSK receiver S1C88Family microcomputers LCD controller 32-bit S1C33Family, . 8 2 MCUs Micro Controller Unit 2-1 4-bit Microcomputers , . 26 3 ASSPs Application Specific Standard Products 3-1 LCD Controllers

Text: any bit position within the octet Delineation State Machine with Hunt, Pre-sync, Sync, LCD Defect, LCD Defect Pre-sync and LCD Defect Verify states Correction and Detection states within the Sync , process specified in ATM UNI 3.1 Indicates Loss of Cell Delineation ( LCD ) status change and Out of Cell , Specification Design File Formats EDIF Netlist cc200.ucf Constraints File Behavioral VHDL Testbench, Verification Tool test scripts Instantiation Templates VHDL , Verilog Reference designs & ITU I

The TFT LCD Controller Reference Designs from Digital Blocks enables hardware designers to accelerate the design-in of TFT LCD panel displays into their system. The Reference Design centers on Digital Blocks DB9000 family of TFT LCD Controller IP Cores, with the DB9000AXI4 Reference Design targeting Altera Cyclone V and Xilinx Zynq FPGAs with the AXI Interconnect and the DB9000AVLN Reference Design targeting all Altera FPGAs with the NIOS II and the Qsys Integration Tool.

The DB9100 BitBLT Reference Design — and optionally the DB9000 TFT LCD Controller –along with an ARM / NIOS II / MicrBlaze embedded microprocessor enable a higher integrated Graphics Subsystem within a single FPGA / ASIC / ASSP device.

Digital Blocks I2C Controller Reference Designs encompass our wide selection of I2C Master/Slave, I2C Master only, and I2C Slave only IP Cores. Please view our offerings and contact Digital Blocks with your requirements.

Digital Blocks SPI Controller Reference Designs encompass our wide selection of SPI Master/Slave, SPI Master only, and SPI Slave only IP Cores. Please view our offerings and contact Digital Blocks with your requirements.

Digital Blocks is the industry leader in providing cycle-accurate Intel® 8259, 8255,and 8279 IP Core Peripheral Replacements as VHDL or Verilog soft cores in CPLDs , FPGAs, ASICs, and ASSP devices.

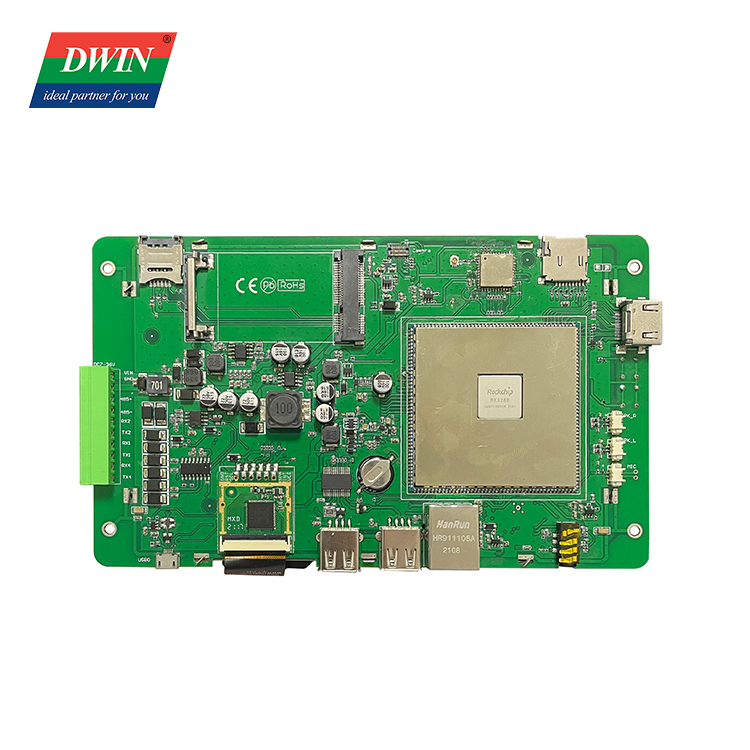

Digital View’s SVX-1920v3 is a full featured LCD controller that is a suitable fit for an extensive range of professional display applications. This is an advanced LCD controller that is ideal for use with high resolution

Digital View"s ALR-1400v2 is a multi-purpose LCD controller that was designed for industrial LCD monitors and can be used for a number of industrial and commercial display applications. Features: ∙ Compact Design ∙

Digital View’s ALR-1920-120 is a multi-purpose LCD controller board with a comprehensive selection of built-in features and control options. This solution is compatible with 120Hz panels with up to 1920x1200 resolution.

The 4169900XX-3 / SP-1600 Controller is end of life (EOL) as of September 15, 2017. The last time buy (LTB) date is/was October 1, 2017. The suggested replacement is the SP-1920. Features: ∙ 10-bit ∙ LVDS

Digital View’s SVH-1920v2 LCD controller is the updated replacement for the SVH-1920. This newer version includes the same signal inputs and mountings as the original with the addition of an eDP panel connection and increased

The 4171400XX-3 / DVS-1600 Controller is end of life (EOL) as of September 15, 2017. The last time buy (LTB) date is/was October 1, 2017. The suggested replacement is the SP-1920. Features: ∙ 10-bit ∙ LVDS

The 4169901XX-3 / HE-1600 Controller is end of life (EOL) as of September 15, 2017. The last time buy (LTB) date is/was October 1, 2017. The suggested replacement is the SP-1920. Features: ∙ 10-bit ∙ LVDS

Digital View’s HE-1920v2 is the replacement for the HE-1920. It is a harsh environment LCD controller with ceramic capacitors and unmatched durability. The HE-1920v2 has a conformal coating layer that preserves the components

The HLR-1920 by Digital View is a compact, wide temperature LCD controller great for general purpose solutions. It is compatible with LCD panels up to 1920x1200 resolution. The HLR-1920 features low signal latency from input

The 4172200XX-3 / AVP-1600 Controller is end of life (EOL) as of September 15, 2017. The last time buy (LTB) date is/was October 1, 2017. The suggested replacement is the SP-1920. Features: ∙ 10-bit ∙ LVDS

Digital View’s SVX-2560 is an advanced LVDS and eDP panel LCD controller. It works with LCD panel resolutions up to 2560x1600 and 1920x1920 and is compatible with video signals up to 2560x1600. Features: ∙ LCD

Digital View"s SVX-4096 is an advanced LCD controller ideal for 4K LCDs. It is compatible with LCD and OLED panel resolutions up to 4096x2160 and video signals up to 4096x2160. Because it is a 4K LCD controller, it is an ideal

The Digital View HX-4096 is a harsh environment 4k LCD controller. It supports video signals up to 4096 x 2160 and LCD panel resolutions up to 4096 x 2160. Because of its conformal coating and extended temperature range,

Digital View’s HSP-1920 is the durable, harsh environment version of the SP-1920 LCD controller. It is supports input and panel activity for video signals up to 1920x1200. The built-in H.246 failover media player makes

Digital View’s ALT-1920 is a compact, general solution LCD controller that covers three popular input formats including HDMI, Analog RGB (VGA), and DisplayPort. It is equipped with ceramic capacitors for improved reliability

The Digital View SP-4096 is an easy-to-use controller board for 4k LCDs. It supports LCD panels and video output of up to 4096 x 2160 resolution. Because of its high resolution and excellent reliability, this 4k LCD controller

The Digital View HSP-4096 is the harsh environment version of the SP-4096 and includes a conformal coating that provides increased resistance to the elements. It supports video signals up to 4096 x 2160 and LCD panel resolutions

The Digital View SVX-4096-120 is an advanced controller board that can support both LCD and OLED panels up to 4096 x 2160 resolution. Because of its super high resolution, this 4k controller board is ideal for commercial

The Digital View DT-4096 is a compact and easy-to-use controller board that supports LCD panels up to 4096 x 2160 resolution. Because of its extensive image control options and super high resolution, this 4k controller

The main part of the architecture is the uBlaze microcontroller. It is connected to many GPIO peripherals for controlling LEDs, 7Segment, Image RAM content and for reading both from DIP Switches and from graphics controller the current line and column for debug. To uBlaze is connected also the interrupt controller as a peripheral. Push buttons and internal timer are connected to interrupt controller.

Another important part of the architecture is Image RAM memory. The RAM memory is described by a vhdl code and is a simple dual RAM memory. This RAM contains the image graphics controller will display on LCD. The size of the image stored in RAM memory depends on the virtual size of the LCD. The VmodTFT LCD has 272 lines and 480 columns and a colour depth of 8 bits for each primary colour. The number of cells of the RAM memory is 130560 and each one contains the data on 24 bits. Therefore the size of the LCD is roughly 3Mb. It requires 96 BRAM block out of 135 the Artix7 FPGA has. The Image RAM memory is interfacing with Pixel Controller GPIO peripheral of uBlaze. This peripheral writes on RAM the value of each pixel. This is connected to port A of uBlaze. The port B of the RAM is connected to graphic controller.

The next part of the system architecture is graphics controller. The latter accesses the Image RAM Port B with the signal address and the Port B output is connected to its RGBin input. The graphics controller is also connected to the VmodMIB via the Pmod connectors in order to set each pixel value of the display.

Ms.Josey

Ms.Josey

Ms.Josey

Ms.Josey