oxide tft lcd factory

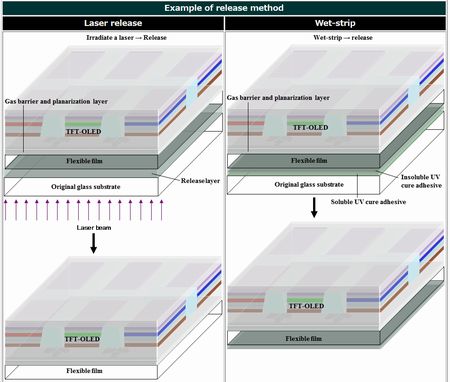

Resin is coated on support substrate and cured, and then, oxide TFT and device are manufactured on resin film, finally, support substrate is released (The resin film is used as substrate)

Oxide thin-film transistor (TFT) liquid crystal display (LCD) panels are increasingly adopted in mobile PCs due to their feature of high resolution while consuming low power. Global shipments of large oxide TFT LCD panels of 9 inches or larger are expected to grow from 20 million units in 2016 to 55.6 million units in 2017, according to new analysis from IHS Markit (Nasdaq: INFO). Of those, 51 million units are estimated to be applied to mobile PCs, which include notebook PCs and tablet PCs, up 200 percent from 17 million units in 2016.

“Demand for high-resolution panels has increased as media content for mobile PCs became available in higher resolutions,” said David Hsieh, senior director at IHS Markit. “Apple’ and Microsoft’s use of oxide TFT LCD panels for products – iPad, iPad Pro, and Surface, respectively – helped increase the oxide mobile PC panel market and encouraged other PC brands to follow suit.”

Low-temperature polysilicon (LTPS) and oxide TFT LCD solutions are major candidates for displaying high-resolution images, and they are expected to account for more than 19 percent of the entire mobile PC display market in 2017, according to the Large Area Display Market Tracker by IHS Markit.

While LTPS can deliver higher resolution images and consume less power than oxide TFT LCD or a-Si TFT LCD, it has its own limits: its production cost is high and the yield rate is low. In addition, it is less efficient to produce large panels. Albeit not as high resolution as LTPS, oxide TFT LCD panels still display high-resolution images better than the a-Si solution, and they are suitable to produce large panels at lower production cost than LTPS.

LG Display and Sharp have expanded their oxide mobile PC panel shipments aggressively by 180 percent and 370 percent, respectively. CEC Panda in China is estimated to increase its shipments from about 600,000 units in 2016 to 4.2 million in 2017. As some oxide panel suppliers are reducing their focus on the mobile PC display business, display makers in China and Taiwan, such as BOE and Innolux, are expected to produce more oxide panels in future, IHS Markit said.

The display industry is continuing to move toward mid-to-large-size, immersive displays in high-performance tablets, notebooks and 8K TVs. As these trends become industry standards, the oxide market emerges as an important opportunity for enabling the next-generation of high-performance displays. These displays feature: higher resolution and faster refresh rates; enhanced circuitry integration to achieve slim bezels; and cost savings for panel makers by improving the panel aperture ratio and enabling large gen size manufacturing.

To achieve these technical requirements, new breakthroughs are needed in thin-film-transistor (TFT) technologies. Among the display industry’s current offerings, amorphous silicon TFT (a-Si TFT) maintains a leading position among all applications, while low-temperature poly-silicon TFT (LTPS) is the predominant display technology for enabling high-performance handheld displays. The key differences between a-Si and LTPS are that an a-Si TFT has a simpler process, structure, and is easier to scale up in terms of manufacturing. However, LTPS offers better TFT performance to achieve higher resolutions and lower power consumption. The drawbacks of LTPS come in size limitations and increased manufacturing costs. For these reasons, neither a-Si or LTPS can fully meet the technical requirements for this next generation of high-performance displays.

All of these industry requirements create new process and glass composition challenges, which present the need to develop an advanced oxide TFT glass technology.

For decades, the dominant technology for flat panel displays was an amorphous silicon (a-Si) backplane. The vast majority of displays were made using a-Si backplanes due to the simplicity in manufacturing process, good economics, and scalability to larger sizes. As demands for brighter and/or higher resolution displays grew due to the introduction and proliferation of handheld mobile devices, alternative backplane technologies, such as low temperature polysilicon (LTPS), became more prevalent. LTPS is similar to a-Si, but requires higher processing temperatures and a more complicated manufacturing process. This results in advanced properties for the backplane, such as >50X higher electronic mobility. These properties allow smaller TFTs (enabling higher resolutions and brighter displays) and faster refresh rates. While clearly a superior technology to a-Si, the higher temperatures and more complex manufacturing process make LTPS considerably more expensive than a-Si. Additionally, LTPS is not easily scaled to larger sizes to enable better panel economics.

The ideal backplane technology would combine the simplicity, economics, and scalability to larger panel sizes of a-Si with the heightened performance of LTPS. This is exactly what oxide TFT technologies offer. The most commonly implemented oxide TFT technology is based on Indium-Gallium-Zinc-Oxide or “IGZO” technologies.

Though the mobility of oxide TFT is not as high as LTPS, it is an order of magnitude better than a-Si technology and capable of driving OLED displays and 8K 120Hz + LCD TVs. Additionally, the low off-current of an oxide TFT could enable low refresh frequency without flicker effects on static images (a comparison of different TFT technologies are shown in Table 1). While, like LTPS, oxide TFT backplanes have improved electrical properties relative to a-Si backplanes, oxide TFT backplanes can scale up to Gen 10.5 at reasonable costs (unlike LTPS), thereby enabling high-end, large-size LCD and OLED TVs. It is for this “just right” compromise of a-Si and LTPS properties that oxide TFT is garnering so much attention from panel makers worldwide. It offers the ability to manufacture displays far superior to a-Si at sizes and costs unachievable by LTPS.

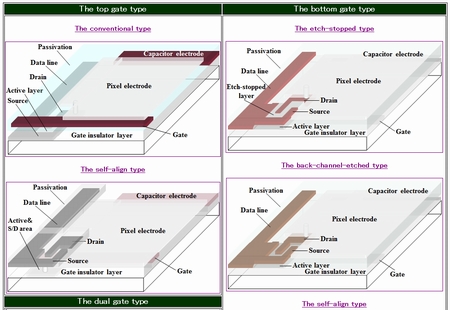

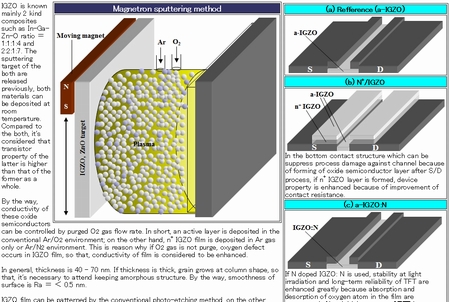

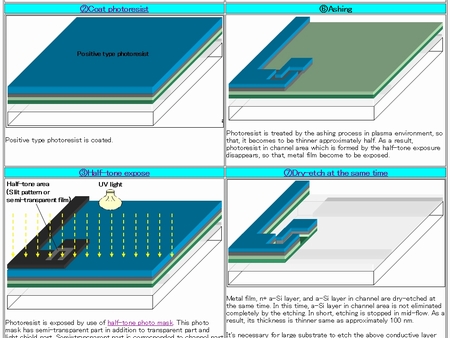

There are two major oxide TFT processes to consider: etch-stop and back channel etch (BCE). The key difference between the processes is the use of an etch-stop layer, also known as ESL, that is required to protect the IGZO channels during the etching process.

Oxide TFT reliability was the major concern in early stage of oxide TFT development. The oxide TFT channel was usually damaged in subsequent processes, so an etch stop structure was designed to protect the oxide TFT channel. The etch-stop (ESL) oxide TFT manufacturing process begins with a bottom gate structure which is covered by a gate insulator and TFT islands. After the gate insulator (GI) layers and TFT patterning, a patterned SiO2 layer is deposited to cover the IGZO channel area in order to protect oxide TFT from following source/drain (S/D) etching. This enables better TFT reliability, and after the S/D etching, then followed by passivation, ITO layer as the Figure 1 shows. In the ESL process, temperatures may go up to 300-400°C for up to an hour or more. While these are higher temperatures than some a-Si processes, it is considerably lower than the typical LTPS processes that can exceed 500°C.

The BCE oxide TFT process (Figure 2) is very similar to the ESL oxide TFT process in the first two photo etching processes (PEP) steps. However, a high temperature (400-500°C) annealing process enhances the TFT reliability that allows the removal of the ESL. The higher temperature annealing step requires a thermally stable glass that can withstand harsh manufacturing environments and processing times relative to the conventional oxide (ESL) or a-Si processes.

To panel makers, the BCE oxide TFT process is similar to the a-Si process, which has been widely used for the past two decades. Also, there is one photo-mask process reduction compared to the ES oxide TFT process, therefore, BCE oxide TFT is becoming a mainstream process of oxide TFT manufacturing.

While the oxide TFT process has clear technical benefits for the manufacture of large and high-performance TVs, it presents a unique set of challenges for the glass substrate used in the process.

When put through a typical TFT backplane process, glass substrates will change shape or size (i.e., strain) which is called a change in total pitch (TP). One of the most important glass substrate attributes is total pitch variation (TPV), which is the deviation from predictable glass movement within a glass sheet and from sheet-to-sheet. For a glass substrate to have good TPV performance, the substrate must have the required balance of physical properties to resist the various causes of strain of the substrate: elastic distortion, stress relaxation, and compaction. These sources of strain, and the corresponding glass property that resists them, are discussed below.

In TFT processes, there are several sources of stress applied to the glass substrate, such as film stresses and gate metals. In oxide TFT, the latter is particularly significant due to the substantial thickness and covered area of the gate metal. The pitch change associated with these stresses is determined by the size of the stress, the elastic modulus of the glass, and the thickness of the substrate. Since the stresses are determined by the TFT manufacturer and the industry is continually driving to thinner and thinner substrates, the only attribute within the control of the glass manufacturer is to increase the elastic modulus to increase the stiffness of the substrate. Also, because the stresses in the TFT process can vary across a sheet or sheet-to-sheet, a higher elastic modulus will reduce the strain due to variations in the applied stresses, thereby minimizing TPV from this potential cause.

The stresses from applied films and gate metal can also contribute to the overall TPV through the relaxation of those stresses during subsequent thermal treatments. As the substrate progresses through the various steps of the TFT process, the films, gate metal, and substrate itself will all undergo stress relaxation. As the stress state of the composite changes with time and temperature, the concomitant strain will accordingly change, causing a pitch change and an increase in TPV. The glass substrate resists this stress relaxation in proportion to its effective viscosity at the process temperatures. In a-Si TFT processes, the temperatures are low enough that there is a minimal amount of stress relaxation due to the glass substrate having a relatively high viscosity at these low temperatures (the viscosity of the glass increases as the temperature decreases). In oxide TFT processing, however, temperatures are higher and, therefore, the potential for stress relaxation is greater due to the lower effective viscosity of the glass. This is particularly acute for the BCE oxide TFT process, which has process steps with temperatures in excess of 400°C. Traditional glass substrates which are sufficient for the typical a-Si applications may also be sufficient for the lower temperature ESL oxide TFT processes. However, the higher temperature BCE oxide TFT process may require a substrate with a higher effective viscosity at temperatures in the range of 400°C.

The effective viscosity of the glass substrate also plays a role in the amount of viscous relaxation the glass substrate undergoes in the TFT process due to structural relaxation of the glass itself. This is commonly referred to as “compaction” or “shrinkage” in the glass industry. Compaction is due to the evolution of the glass structure from a non-equilibrium state toward a structure closer to equilibrium with the customer process. The amount of this viscous relaxation that occurs is proportional to the degree to which the glass is out of equilibrium, and inversely proportional to the effective viscosity of the glass at the TFT process temperatures. Consequently, a higher viscosity glass is beneficial for minimizing TPV, just like in stress relaxation. In glass property terms, a higher viscosity glass is a glass with a higher “annealing point” therefore glass manufacturers will often tout the high annealing point of their glass compositions.

Corning’s proprietary fusion process manufactures glass panels at Gen 10.5 sizes (2940 x 3370mm), enabling higher glass utilization for larger-screen sizes. For example, one sheet of Gen 10.5 glass could create eight 65” display panels, or six 75” display panels. This enhanced glass utilization greatly reduces cost for panel makers and is key for enabling the oxide TFT market"

For oxide TFT to be used in IT or handheld products, one of the key features is a thin and light form factor. To achieve this, the display panel usually needs to be thinned down to roughly 0.15mm / 0.15mm (for the two pieces of glass in the display) using the chemical slimming process. A faster etch rate is clearly desired to enable higher throughput and lower costs but this often comes at the cost of the generation of “sludge.” Sludge can create problems in the etch vendors’ processes and end up causing more cost than the fast etch rate reduced. By using a glass that balances maximizing etch rate while minimizing sludge generation, panel makers optimize their throughput and costs.

The technology challenges and technical requirements outlined fuel an industry need for a new glass substrate with the right balance of physical properties for oxide TFT technology. For displays applications, this includes low total pitch variation, low total thickness variation, and low sag. This package of glass attributes, alongside the ability to scale-up manufacturing to large-gen sizes, will help enable the next-generation of mid-to-large-size, immersive displays in 8K TVs.

These applications require a shift toward oxide technology, versus the current a-Si and LTPS TFT technologies. As the push for oxide increases, new process and technical challenges emerge for panel makers. To build a display that meets these performance expectations, panel makers require a thermally and dimensionally stable glass to improve yields while achieving the desired resolution.

An oxide thin-film transistor (TFT) is one of the TFT technologies. Depending on the semiconductor material and properties, TFTs can be classified as amorphous silicon (a-Si), LTPS, and oxide TFTs. An oxide TFT is also used for switching and adjustment of pixel brightness. An oxide TFT, in the manufacturing process, converts ‘Indium-Gallium-Zinc (In-Ga-Zn)’ source material into an oxide that has the properties of a semiconductor (In-Ga-Zn-Oxygen), and hence the name an ‘oxide’ TFT.

As with amorphous silicon (a-Si), an oxide TFT is amorphous. However, the electron mobility in an oxide TFT is roughly 10 times as fast as the ones in amorphous silicon (a-Si), and therefore, an oxide TFT has a greater ability to manufacture displays with higher resolutions. Thanks to the high electron mobility, an oxide TFT has an advantage in integrating TFT circuits, increasing the usable space, and making the bezel thinner.

Compared to the low-temperature polysilicon (LTPS), the electron mobility in an oxide TFT is slower, but a significant portion of equipment used for the existing a-Si manufacturing process can be used for oxide TFTs, giving the oxide TFT a comparative advantage in production costs. In addition, an oxide TFT — unlike the LTPS — does not involve the excimer laser annealing (ELA) process, which removes restrictions in size that arise from the crystallization process, and the great uniformity thanks to its amorphous nature makes an oxide TFT suitable for large-sized displays.

4.5.Comparing the key attributes of different TFT technologies (a-Si, pc-Si, nc-Si, OTFT, graphene, CNT, etc). Parameters include manufacturing technique, mobility, uniformity, stability, and commercialisation stage and primary uses

7.1.Radar chart assessing the merits of different backplane technologies (LTPS, oxide, a-Si, organics) for LCD displays. The parameters considered are resolution, size, flexibility, on-pixel processing, and 3D. Here, the scale is from

7.2.Radar chart assessing the merits of different backplane technologies (LTPS, oxide, a-Si, organics) for OLED displays. The parameters considered are resolution, size, flexibility, on-pixel processing, and 3D. Here, the scale is fro

7.7.Announced annual production capacity (area) of various OLED display manufactures in 2015-2016. Two categories are developed: 1) LTPS backplanes and 2) oxide backplanes

A thin-film transistor (TFT) is a special type of field-effect transistor (FET) where the transistor is thin relative to the plane of the device.substrate. A common substrate is glass, because the traditional application of TFTs is in liquid-crystal displays (LCDs). This differs from the conventional bulk metal oxide field effect transistor (MOSFET), where the semiconductor material typically is the substrate, such as a silicon wafer.

TFTs can be fabricated with a wide variety of semiconductor materials. Because it is naturally abundant and well understood, amorphous or polycrystalline silicon was historically used as the semiconductor layer. However, because of the low mobility of amorphous siliconcadmium selenide,metal oxides such as indium gallium zinc oxide (IGZO) or zinc oxide,organic semiconductors,carbon nanotubes,metal halide perovskites.

Because TFTs are grown on inert substrates, rather than on wafers, the semiconductor must be deposited in a dedicated process. A variety of techniques are used to deposit semiconductors in TFTs. These include chemical vapor deposition (CVD), atomic layer deposition (ALD), and sputtering. The semiconductor can also be deposited from solution,printing

Some wide band gap semiconductors, most notable metal oxides, are optically transparent.electrodes, such as indium tin oxide (ITO), some TFT devices can be designed to be completely optically transparent.head-up displays (such as on a car windshield).The first solution-processed TTFTs, based on zinc oxide, were reported in 2003 by researchers at Oregon State University.Universidade Nova de Lisboa has produced the world"s first completely transparent TFT at room temperature.

The best known application of thin-film transistors is in TFT LCDs, an implementation of liquid-crystal display technology. Transistors are embedded within the panel itself, reducing crosstalk between pixels and improving image stability.

As of 2008LCD TVs and monitors use this technology. TFT panels are frequently used in digital radiography applications in general radiography. A TFT is used in both direct and indirect capturemedical radiography.

The most beneficial aspect of TFT technology is its use of a separate transistor for each pixel on the display. Because each transistor is small, the amount of charge needed to control it is also small. This allows for very fast re-drawing of the display.

In February 1957, John Wallmark of RCA filed a patent for a thin film MOSFET in which germanium monoxide was used as a gate dielectric. Paul K. Weimer, also of RCA implemented Wallmark"s ideas and developed the thin-film transistor (TFT) in 1962, a type of MOSFET distinct from the standard bulk MOSFET. It was made with thin films of cadmium selenide and cadmium sulfide. In 1966, T.P. Brody and H.E. Kunig at Westinghouse Electric fabricated indium arsenide (InAs) MOS TFTs in both depletion and enhancement modes.

The idea of a TFT-based liquid-crystal display (LCD) was conceived by Bernard J. Lechner of RCA Laboratories in 1968.dynamic scattering LCD that used standard discrete MOSFETs, as TFT performance was not adequate at the time.T. Peter Brody, J. A. Asars and G. D. Dixon at Westinghouse Research Laboratories developed a CdSe (cadmium selenide) TFT, which they used to demonstrate the first CdSe thin-film-transistor liquid-crystal display (TFT LCD).electroluminescence (EL) in 1973, using CdSe.active-matrix liquid-crystal display (AM LCD) using CdSe in 1974, and then Brody coined the term "active matrix" in 1975.

A breakthrough in TFT research came with the development of the amorphous silicon (a-Si) TFT by P.G. le Comber, W.E. Spear and A. Ghaith at the University of Dundee in 1979. They reported the first functional TFT made from hydrogenated a-Si with a silicon nitride gate dielectric layer.research and development (R&D) of AM LCD panels based on a-Si TFTs in Japan.

By 1982, Pocket TVs based on AM LCD technology were developed in Japan.Fujitsu"s S. Kawai fabricated an a-Si dot-matrix display, and Canon"s Y. Okubo fabricated a-Si twisted nematic (TN) and guest-host LCD panels. In 1983, Toshiba"s K. Suzuki produced a-Si TFT arrays compatible with CMOS integrated circuits (ICs), Canon"s M. Sugata fabricated an a-Si color LCD panel, and a joint Sanyo and Sanritsu team including Mitsuhiro Yamasaki, S. Suhibuchi and Y. Sasaki fabricated a 3-inch a-SI color LCD TV.

The first commercial TFT-based AM LCD product was the 2.1-inch Epson ET-10Hitachi research team led by Akio Mimura demonstrated a low-temperature polycrystalline silicon (LTPS) process for fabricating n-channel TFTs on a silicon-on-insulator (SOI), at a relatively low temperature of 200°C.Hosiden research team led by T. Sunata in 1986 used a-Si TFTs to develop a 7-inch color AM LCD panel,Apple Computers.Sharp research team led by engineer T. Nagayasu used hydrogenated a-Si TFTs to demonstrate a 14-inch full-color LCD display,electronics industry that LCD would eventually replace cathode-ray tube (CRT) as the standard television display technology.notebook PCs.IBM Japan introduced a 12.1-inch color SVGA panel for the first commercial color laptop by IBM.

TFTs can also be made out of indium gallium zinc oxide (IGZO). TFT-LCDs with IGZO transistors first showed up in 2012, and were first manufactured by Sharp Corporation. IGZO allows for higher refresh rates and lower power consumption.polyimide substrate.

Petti, Luisa; Münzenrieder, Niko; Vogt, Christian; Faber, Hendrik; Büthe, Lars; Cantarella, Giuseppe; Bottacchi, Francesca; Anthopoulos, Thomas D.; Tröster, Gerhard (2016-06-01). "Metal oxide semiconductor thin-film transistors for flexible electronics". Applied Physics Reviews. 3 (2): 021303. Bibcode:2016ApPRv...3b1303P. doi:10.1063/1.4953034.

Kawamoto, H. (2012). "The Inventors of TFT Active-Matrix LCD Receive the 2011 IEEE Nishizawa Medal". Journal of Display Technology. 8 (1): 3–4. Bibcode:2012JDisT...8....3K. doi:10.1109/JDT.2011.2177740. ISSN 1551-319X.

Morozumi, Shinji; Oguchi, Kouichi (12 October 1982). "Current Status of LCD-TV Development in Japan". Molecular Crystals and Liquid Crystals. 94 (1–2): 43–59. doi:10.1080/00268948308084246. ISSN 0026-8941.

Mimura, Akio; Oohayashi, M.; Ohue, M.; Ohwada, J.; Hosokawa, Y. (1986). "SOI TFT"s with directly contacted ITO". IEEE Electron Device Letters. 7 (2): 134–6. Bibcode:1986IEDL....7..134M. doi:10.1109/EDL.1986.26319. ISSN 0741-3106. S2CID 36089445.

Sunata, T.; Yukawa, T.; Miyake, K.; Matsushita, Y.; Murakami, Y.; Ugai, Y.; Tamamura, J.; Aoki, S. (1986). "A large-area high-resolution active-matrix color LCD addressed by a-Si TFT"s". 33 (8): 1212–1217. Bibcode:1986ITED...33.1212S. doi:10.1109/T-ED.1986.22644. ISSN 0018-9383. S2CID 44190988.

Sunata, T.; Miyake, K.; Yasui, M.; Murakami, Y.; Ugai, Y.; Tamamura, J.; Aoki, S. (1986). "A 640 × 400 pixel active-matrix LCD using a-Si TFT"s". IEEE Transactions on Electron Devices. 33 (8): 1218–21. Bibcode:1986ITED...33.1218S. doi:10.1109/T-ED.1986.22645. ISSN 0018-9383. S2CID 6356531.

Nagayasu, T.; Oketani, T.; Hirobe, T.; Kato, H.; Mizushima, S.; Take, H.; Yano, K.; Hijikigawa, M.; Washizuka, I. (October 1988). "A 14-in.-diagonal full-color a-Si TFT LCD". Conference Record of the 1988 International Display Research Conference: 56–58. doi:10.1109/DISPL.1988.11274. S2CID 20817375.

The most common semiconducting layer is made of amorphous silicon (a-Si). a-Si thin film transistor - liquid crystal display (TFT-LCD) has been the dominant technology for the manufacturing of active matrix TFT-LCD for over 20 years. a-Si is a low cost material in abundant supply.

a-Si is a low cost material in abundant supply. However, the electron mobility of a-Si is very low (around 1cm2/Vs) and can’t physically support high refresh rates such as the 240Hz needed for HDTV. Due to their high electron mobility, new materials such as metal oxide (MO) and low temperature polysilicon (LTPS) are now replacing a-Si to manufacture the industry’s two main types of screens: LCD and organic light-emitting diode (OLED) displays.

Chinese display maker CSOT has placed orders for equipment to use in the production of large liquid crystal display (LCD) panels, TheElec has learned.

The company has recently placed orders for use at its Gen 8.6 (2250x2600mm) oxide thin-film transistor (TFT) LCD production line at its T9 factory in Guangzhou, people familiar with the matter said.

Oxide TFT offers fast electron movement and is power efficient. The technology is used in high-end LCD panels __ low-end LCD panels use a-Si TFT. LG Display also sues oxide TFT for the production of its large OLED panels.

At its T9 factory, the company is planning to manufacture LCD panels for TVs, IT products and automobiles, which means it will be competing with market leaders BOE and LG Display in the sectors.

TFT-LCD was invented in 1960 and successfully commercialized as a notebook computer panel in 1991 after continuous improvement, thus entering the TFT-LCD generation.

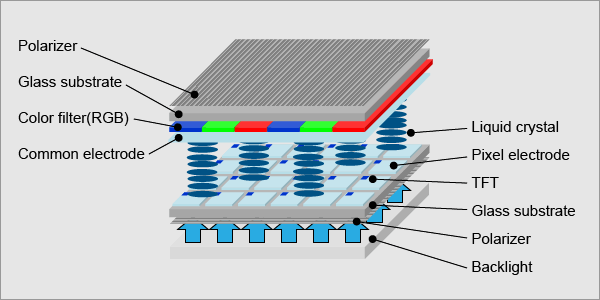

Simply put, the basic structure of the TFT-LCD panel is a layer of liquid crystal sandwiched between two glass substrates. The front TFT display panel is coated with a color filter, and the back TFT display panel is coated with a thin film transistor (TFT). When a voltage is applied to the transistor, the liquid crystal turns and light passes through the liquid crystal to create a pixel on the front panel. The backlight module is responsible for providing the light source after the TFT-Array panel. Color filters give each pigment a specific color. The combination of each different color pixel gives you an image of the front of the panel.

The TFT panel is composed of millions of TFT devices and ITO (In TI Oxide, a transparent conductive metal) regions arranged like a matrix, and the so-called Array refers to the region of millions of TFT devices arranged neatly, which is the panel display area. The figure below shows the structure of a TFT pixel.

No matter how the design of TFT display board changes or how the manufacturing process is simplified, its structure must have a TFT device and control liquid crystal region (if the light source is penetration-type LCD, the control liquid crystal region is ITO; but for reflective LCD, the metal with high reflection rate is used, such as Al).

The TFT device is a switch, whose function is to control the number of electrons flowing into the ITO region. When the number of electrons flowing into the ITO region reaches the desired value, the TFT device is turned off. At this time, the entire electrons are kept in the ITO region.

The figure above shows the time changes specified at each pixel point. G1 is continuously selected to be turned on by the driver IC from T1 to TN so that the source-driven IC charges TFT pixels on G1 in the order of D1, D2, and Dn. When TN +1, gATE-driven IC is selected G2 again, and source-driven IC is selected sequentially from D1.

Many people don’t understand the differences between generations of TFT-LCD plants, but the principle is quite simple. The main difference between generations of plants is in the size of glass substrates, which are products cut from large glass substrates. Newer plants have larger glass substrates that can be cut to increase productivity and reduce costs, or to produce larger panels (such as TFT display LCD TV panels).

The TFT-LCD industry first emerged in Japan in the 1990s, when a process was designed and built in the country. The first-generation glass substrate is about 30 X 40 cm in size, about the size of a full-size magazine, and can be made into a 15-inch panel. By the time Acer Technology (which was later merged with Unioptronics to become AU Optronics) entered the industry in 1996, the technology had advanced to A 3.5 generation plant (G3.5) with glass substrate size of about 60 X 72 cm.Au Optronics has evolved to a sixth-generation factory (G6) process where the G6 glass substrate measures 150 X 185 cm, the size of a double bed. One G6 glass substrate can cut 30 15-inch panels, compared with the G3.5 which can cut 4 panels and G1 which can only cut one 15-inch panel, the production capacity of the sixth generation factory is enlarged, and the relative cost is reduced. In addition, the large size of the G6 glass substrate can be cut into large-sized panels, which can produce eight 32-inch LCD TV panels, increasing the diversity of panel applications. Therefore, the global TFT LCD manufacturers are all invested in the new generation of plant manufacturing technology.

The TRANSISTor-LCD is an acronym for thin-film TFT Display. Simply put, TFT-LCD panels can be seen as two glass substrates sandwiched between a layer of liquid crystal. The upper glass substrate is connected to a Color Filter, while the lower glass has transistors embedded in it. When the electric field changes through the transistor, the liquid crystal molecules deflect, so as to change the polarization of the light, and the polarizing film is used to determine the light and shade state of the Pixel. In addition, the upper glass is fitted to the color filter, so that each Pixel contains three colors of red, blue and green, which make up the image on the panel.

The organic light display can be divided into Passive Matrix (PMOLED) and Active Matrix (AMOLED) according to the driving mode. The so-called active driven OLED(AMOLED) can be visualized in the Thin Film Transistor (TFT) as a capacitor that stores signals to provide the ability to visualize the light in a grayscale.

Although the production cost and technical barriers of passive OLED are low, it is limited by the driving mode and the resolution cannot be improved. Therefore, the application product size is limited to about 5″, and the product will be limited to the market of low resolution and small size. For high precision and large picture, the active drive is mainly used. The so-called active drive is capacitive to store the signal, so when the scanning line is swept, the pixel can still maintain its original brightness. In the case of passive drive, only the pixels selected by the scan line are lit. Therefore, in an active-drive mode, OLED does not need to be driven to very high brightness, thus achieving better life performance and high resolution.OLED combined with TFT technology can realize active driving OLED, which can meet the current display market for the smoothness of screen playback, as well as higher and higher resolution requirements, fully display the above superior characteristics of OLED.

The technology to grow The TFT on the glass substrate can be amorphous Silicon (A-SI) manufacturing process and Low-Temperature Poly-Silicon (LTPS). The biggest difference between LTPS TFT and A-SI TFT is the difference between its electrical properties and the complicated manufacturing process. LTPS TFT has a higher carrier mobility rate, which means that TFT can provide more current, but its process is complicated.A-si TFT, on the other hand, although a-Si’s carrier movement rate is not as good as LTPS’s, it has a better competitive advantage in cost due to its simple and mature process.Au Optronics is the only company in the world that has successfully combined OLED with LTPS and A-SI TFT at the same time, making it a leader in active OLED technology.

The LTPS membrane is much more complex than a-SI, yet the LTPS TFT is 100 times more mobile than A-SI TFT. And CMOS program can be carried out directly on a glass substrate. Here are some of the features that p-SI has over A-SI:

LCD screens are backlit to project images through color filters before they are reflected in our eye Windows. This mode of carrying backlit LCD screens, known as “penetrating” LCD screens, consumes most of the power through backlit devices. The brighter the backlight, the brighter it will appear in front of the screen, but the more power it will consume.

Cross sectional diagram of typical metal oxide thin film transistor. In this case the "oxide" refers to the semiconducting layer between the source and drain electrodes.

An oxide thin-film transistor (oxide TFT) or metal oxide thin film transistor is a type of thin film transistor where the semiconductor is a metal oxide compound. An oxide TFT is distinct from a metal oxide field effect transistor (MOSFET) where the word "oxide" refers to the insulating gate dielectric (normally silicon dioxide). In an oxide TFT, the word oxide refers to the semiconductor. Oxide TFTs have applications as amplifiers to deliver current to emitters in display backplanes.

The first transistor employing a metal oxide as the semiconductor was reported in 1964 by Klasens and Koelmans at Philips Research Laboratories.Hideo Hosono, who was studying transparent conducting oxides,Oregon State University reported oxide TFTs employing the binary oxide zinc oxide as the semiconductor.

Oxides have several properties which make them desirable over hydrogenated amorphous silicon (a-Si:H), which was the incumbent TFT technology in the early 2000"s.

Most n-type (electron transporting) oxide TFTs employ semiconductors that have a wide bandgap; generally greater than 3 eV. For this reason they are attractive for use in fully transparent electronics. Their wide bandgap also means they have a low off-current, and hence a high on/off ratio; a desirable property for well-defined on- and off-states.

One significant drawback with oxide TFTs is that there are very few p-type (hole transporting) metal oxide semiconductors.complementary logic, and hence information processing.

Metal oxide semiconductors are typically deposited using sputtering, a vacuum-based growth technique resulting in an amorphous or polycrystalline layer. Oxides can also be deposited from solution, such as via spin-coating or spray coating.

Optical and SEM (scanning electron microscopy) images of fabricated (a, b) CL and (c, d) CLSE pixel structures. The five white line patterns in (d) are the ITO interdigitated pixel and common electrodes. (e) Images from the normal direction and from 50 degrees to the left and right of a 2.3-inch-diagonal display incorporating the IPS TFT-LCD panel. (f) The three-black matrix (BM) patterns (top: BM covering both gate and data lines, middle: BM covering only the data lines, and bottom: without BM) and (g) optical images of pixels without BM (left: LC on and off voltages supplied to every other data line, right: LC off voltage supplied to all data lines).

Figure 3e shows images from the normal direction and from 50 degrees to the left and right of a 2.3-inch-diagonal display incorporating the IPS TFT-LCD panel fabricated in our laboratory, (f) the three black matrix (BM) patterns (top: BM covering both gate and data lines, middle: BM covering only the data lines, and bottom: without BM), and (g) optical images of panel areas without the BM (left: LC on and off voltages supplied to every other data line, right: LC off voltage supplied to all data lines). As can be seen in the image from the normal direction, the brightness and contrast of the display area with the top BM and middle BM patterns are almost the same, but the contrast of the display area without the BM is relatively lower because of the lower darkness level of the LC off pixels indicating “HITACHI”. As shown in Fig. 3g, this is due to light leaking through the aperture between the data line and adjacent common lines. Therefore, in the CL structure, the BM on the drain line is necessary to obtain a high contrast ratio by shielding light leakage. This is the same as in the conventional structure. On the contrary, there is no light leakage along the gate line through the gaps between the gate line and edges of the pixel/common electrodes, as is clearly shown in Fig. 3g. This is a unique advantage of the CL structure because the conventional structure must shield these gaps with the BM to prevent light leakage. The suppression of light leakage along the gate line in the CL structure is due to the driving scheme (see Fig. 2b,a for a comparison with the conventional structure). During the holding period (tOFF) in the conventional structure, regardless of the pixel voltage, Vp (including Vp = 0), nonzero Vgp and Vgc are always applied to keep the TFT off, and these voltages are applied to the LC layer, inducing light leakage as reported in

Figure 4a shows the gate voltage (Vg) dependence of the panel brightness, while the inset shows that of the TFT current (transfer characteristics). The gray curves are for the conventional IPS TFT-LCD with the TFT before enhancement, the common line, and the matrix BM (MBM) shown at the top of Fig. 3f. The blue curves are for the proposed CL structure with the enhanced TFT and the stripe BM (SBM) shown in the middle of Fig. 3f. In this case, enhanced TFT characteristics were obtained by using an MNOS TFT without back-channel oxidation that was enhanced by the BTS process. In both structures, the threshold voltages for panel brightness, defined by extrapolating the straight part of the brightness curves, reflect those of the TFT transfer curves defined as Vg at a drain current of 10−12 A, and they are well matched to be 4 V and 9 V, respectively. The maximum brightness for the CL structure is 137% higher than that for the conventional structure, which is due to the increase in the aperture ratio from 38 to 52% that results from the elimination of the common line and the BM covering the gate line.

(a) Dependence of panel brightness and TFT current on gate voltage for the conventional pixel structure of 38% aperture ratio (AR) with matrix black matrix (MBM) over both drain and gate lines and proposed CL pixel structure of 52% AR with strip black matrix (SBM) over only the drain lines. Transfer characteristics before and after bias temperature stress (BTS) treatment are shown in the inset. (b) Charging and (c) holding characteristics of enhanced TFT of the CL structure with gate as a common line. Vg and Vd in the TFT ON state are 30 V and +/−7 V, respectively.

To estimate the charging and holding characteristics of the MNOS-enhanced TFT in the panel, the gate TFT ON and OFF time dependences of the panel brightness were measured (Fig. 4b,c). The charging characteristics in Fig. 4b are plotted as a function of tON at tOFF = 16.6 ms, Vg = 30 V, and Vd = ± 7 V. The holding characteristics in Fig. 4c are plotted as a function of tOFF at tON = 34 μs. 95.1% charging at tON = 34 μs and 95.3% holding at tOFF = 16.6 ms indicate that the enhanced TFT has sufficient charging and holding performance to drive a standard VGA (640 × 480 pixels) panel (the number of scanning lines is estimated as tOFF/tON = 16.6/0.034 = 488).

To confirm the driving conditions for the CL structure without the BM along the gate line (with the SBM), the tOFF dependence of the contrast ratio (CR) in the CL panel was further investigated as shown in Fig. 5a, where CR is plotted as a function of tOFF for the CL panels with the matrix BM (MBM) and the strip BM (SBM). The inset shows the brightness in the bright (Vd = 7 V) and dark (Vd = 0 V) states of the CL panel with the SBM as a function of tOFF and an optical image of the panel with tOFF = 6.4 ms. The SBM and MBM panels keep CR higher than 240 with tOFF > 16.6 ms, the frame period of a display panel without flicker being noticeable to the human eye. both panels decrease CR when tOFF is less than 16.6 ms; the CR of the SBM panel decreases faster than the CR of the MBM panel. As shown in the inset, the decrease in CR was due to the increase in dark-state brightness with decreasing tOFF as light leakage increases along the gate line. This light leakage is induced by the voltage Vgp = Vgc = VgON = 30 V applied only for 34 μs during the TFT ON (charging) state, which is 1/488th the duration, tOFF = 16.6 ms, of the TFT OFF (holding) state with Vgp = Vgc = VgOFF = 0 V, but the ratio increases with decreasing tOFF and becomes effective enough to switch on LC layer and induce light leakage. However, it should be stressed again that the CL panel with the normal holding (TFT OFF) time of 16.6 ms does not suffer from the light leakage along the gate line, so the aperture ratio can be increased by removing the BM along the gate line.

Figure 6 indicates the effect of bias temperature stress (BTS) on the TFT characteristics. As the stressing time, tS, of the positive gate stress voltage, Vst = + 77 V, increases from 0 to 3600 s, the transfer (Id-Vg) curve shifts in the positive direction (Fig. 6a). Vth is defined as Vg at which Id = 10−12 A and ΔVth is defined as the Vth shift from the initial value via BTS. As shown in Fig. 6b, ΔVth increases logarithmically with increasing tS: ΔVth = 2.17 + 4.93 × log (tS). The mechanism behind the gate-stress-induced Vth shift is electron tunnel injection from the a-Si:H semiconductor into the SiOx gate insulator. For confirmation, ΔVth of MNOS TFTs with different SiOx thicknesses is plotted as a function of the electric field applied to the SiOx layer in Fig. 6c. Here, the thickness of the SiOx was varied (5, 10, 20, 50 nm), while the SiN thickness was fixed at 200 nm. The electric field applied to SiOx, Eox, was calculated using the following equation,

Effect of bias temperature stress (BTS) on TFT characteristics. (a) The transfer (Id–Vg) curve shifts in the positive direction with positive gate bias stress of Vst = + 77 V over the duration of 0–3600 s. (b) ΔVth, defined as the Vth shift from the initial value via BTS, increases logarithmically with increasing tS, following ΔVth = 2.17 + 4.93 × log (tS). (c) ΔVth of MNOS TFTs with different SiOx thicknesses from 5 to 50 nm as a function of the electric field applied to the SiOx layer.

Figure 7a shows the effect of back-channel oxidation (BCO) and passivation (PAS) on the Id-Vg characteristics of the MNOS TFT. The Id-Vg curve with Vth = 5.1 V is further enhanced to Vth = 10.9 V after BCO, although there is a slight degradation of the slope of the current increase in the sub-threshold region. The slope recovers after PAS without any change to the enhanced characteristics

(a) Effect of back-channel oxidation (BCO) and passivation (PAS) on Id–Vg characteristics of MNOS TFT. (b) Vth and Vth standard deviation, σVth, after BTS and after BCO without BTS treatments and (c) SiOX thickness as a function of position along gate-line, x.

The advantage of BCO over BTS is the uniformity of the enhanced characteristics; Fig. 7b shows the distribution of the enhanced Vth as a function of position along gate-line, x, for the MNOS TFTs connected with a 90-mm-long gate line in the TFT substrate after BTS and BCO treatments. The average value of Vth and the standard deviation, σVth, for pristine TFTs before BTS or BCO, are 5.1 V and 0.35 V, respectively. After BCO, Vth is uniformly enhanced, with an average Vth = 11 V and σVth = 0.4 V without increasing σVth. On the other hand, after BTS, Vth is nonuniformly enhanced with an average Vth = 9.3 V and σVth of 1.4 V. In particular, Vth increases linearly as a function of position along gate-line, x. As the gate SiOx thickness linearly decreases, from (54 nm) to (47 nm) with increasing x as shown in Fig. 7c, the increase in ΔVth after BTS with x is due to increase in the electric field applied to SiOx as shown in Fig. 6c and Eq. 1.

It has been shown that the Vth of the MNOS TFT is independent of the gate SiOx thickness when the thickness is more than 5 nm8a, Vth of the MNOS TFT with the BCO treatment becomes almost independent of the BCO SiOx thickness. As shown in the inset, the thickness of BCO SiOx composed of oxidized a-Si:H linearly increases with BCO processing time, and the Vth increase almost saturates at a BCO SiOx thickness greater than 5 nm. Therefore, the enhanced MNOS TFT after BCO has a uniformly high Vth that is robust to thickness fluctuations of the gate and BCO SiOx layers. BCO also has an advantage over BTS in terms of the stability of Vth as shown in Fig. 8b, which plots the annealing time dependence of Vth for BCO and BTS. In this experiment, the stoichiometry (x) of the gate SiOx was 1.78 for BTS and 1.78 and 1.9 for BCO. The annealing temperature in the N2 atmosphere was 200 °C. In the case of BTS, Vth decreased to the pristine value after approximately 5 h of annealing, while Vth decreased more slowly in the case of BCO. In particular, the annealing time required for Vth to fall to 7 V was 7.5 times longer than that of BTS. Increasing the stoichiometry (x) of the gate SiOx dramatically improved the BCO-enhanced Vth to as much as 11 V, which was stably maintained after 24 h of annealing at 200 °C.

(a) Dependence of Vth on thickness of back-channel oxidized (BCO) SiOX. The inset shows the SiOx thickness dependence on the BCO process time for RF powers of 200 W and 500 W. (b) Stability of Vth as a function of annealing time for three different TFTs with gate SiOx stoichiometry, x = 1.78 and bias temperature stress (BTS), x = 1.78 and BCO, and x = 1.9 and BCO. The temperature of annealing in the N2 atmosphere was 200 °C. (c) Band diagram of back-channel oxidized MNOS TFT. The red arrows show the electric dipoles at the SiOX/a-Si:H and a-Si:H/BCO SiOX interfaces.

A schematic band model for the MNOS TFT with the BCO treatment and the sectional structure of the interface between the a-Si:H and gate and BCO SiOx are shown in Fig. 8c. The uniformly high Vth that is independent of SiOx thickness is due to the dipoles generated at the channel and back-channel interfaces between a-Si:H and SiOx8 of reference

The present disclosure relates to a display device, and more particularly, to an oxide thin film transistor (TFT), a method of manufacturing the same, a display panel including the oxide TFT, and a display device including the display panel. Description of the Background

Flat panel display (FPD) devices are applied to various kinds of electronic products such as portable phones, tablet personal computers (PCs), notebook PCs, etc. Examples of the FPD devices include liquid crystal display (LCD) devices, organic light emitting display devices, etc. Recently, electrophoretic display devices (EPDs) are being widely used as a type of FPD device.

In the FPD devices (hereinafter referred to as a display device), the LCD devices display an image by using liquid crystals, and the organic light emitting display devices use a self-emitting device which self-emits light.

A display panel constituting a display device includes a plurality of switching elements for displaying an image. Each of the switching elements includes a TFT. The TFT is formed of amorphous silicon, polysilicon, or an oxide semiconductor. A TFT including the oxide semiconductor is referred to as an oxide TFT.

Particularly, an amorphous oxide TFT is formed through a low temperature film forming process using the sputtering process. In order to manufacture a crystalline oxide TFT, for example, a high temperature film forming process is performed at a temperature of 300 degrees C. or higher, and then, a thermal treatment is additionally performed.

Since the amorphous oxide TFT and the crystalline oxide TFT have different characteristics, the amorphous oxide TFT and the crystalline oxide TFT are individually applied to various fields. Particularly, since the crystalline oxide TFT is good in reliability, the use of the crystalline oxide TFT is increasing.

However, as described above, the high temperature film forming process should be performed for manufacturing the related art crystalline oxide TFT. However, it is difficult for the high temperature film forming process to be applied to a display panel including a large screen.

Accordingly, the present disclosure is directed to provide an oxide TFT, a method of manufacturing the same, a display panel including the oxide TFT, and a display device including the display panel that substantially obviate one or more problems due to limitations and disadvantages of the related art.

An aspect of the present disclosure is directed to provide an oxide TFT, a method of manufacturing the same, a display panel including the oxide TFT, and a display device including the display panel, in which a crystalline oxide semiconductor is provided on a metal insulation layer including metal through a metal organic chemical vapor deposition (MOCVD) process.

To achieve these and other advantages and in accordance with the purpose of the disclosure, as embodied and broadly described herein, there is provided an oxide TFT including a metal insulation layer including metal, a crystalline oxide semiconductor adjacent to the metal insulation layer, a gate including metal, a gate insulation layer between the crystalline oxide semiconductor and the gate, a first conductor in one end of the crystalline oxide semiconductor, and a second conductor in another end of the crystalline oxide semiconductor.

In another aspect of the present disclosure, there is provided an oxide TFT including a metal insulation layer including metal, a crystalline oxide semiconductor on the metal insulation layer, a gate insulation layer on the crystalline oxide semiconductor, a gate on the gate insulation layer, a first conductor in one end of the crystalline oxide semiconductor, and a second conductor in another end of the crystalline oxide semiconductor.

In another aspect of the present disclosure, there is provided an oxide TFT including a gate on a substrate, a gate insulation layer covering the gate, a crystalline oxide semiconductor on the gate insulation layer, a metal insulation layer on the crystalline oxide semiconductor and including metal, a first conductor on one side of the crystalline oxide semiconductor, and a second conductor on another side of the crystalline oxide semiconductor.

In another aspect of the present disclosure, there is provided a method of manufacturing an oxide TFT including depositing metal and an oxide semiconductor, applying heat to the metal and the oxide semiconductor having a non-crystalline structure to change the oxide semiconductor to a crystalline oxide semiconductor, and connecting a first electrode and a second electrode to the crystalline oxide semiconductor.

The depositing of the metal and the oxide semiconductor may include depositing the metal on a substrate and depositing the oxide semiconductor on the metal through an MOCVD process, and the connecting of the first electrode and the second electrode may include depositing a gate insulation layer material on the crystalline oxide semiconductor, depositing a gate material on the gate insulation layer material, etching the gate insulation layer material and the gate material to form a gate insulation layer and a gate, depositing an insulation layer to cover the gate insulation layer and the gate, forming a first contact hole exposing a first conductor provided in one end of the crystalline oxide semiconductor and a second contact hole exposing a second conductor provided in another end of the crystalline oxide semiconductor, in the insulation layer, and forming the first electrode connected to the first conductor through the first contact hole and the second electrode connected to the second conductor through the second contact hole, on the insulation layer.

The depositing of the metal and the oxide semiconductor may include depositing a gate on a substrate, depositing a gate insulation layer to cover the gate, depositing the oxide semiconductor on the metal on the gate insulation layer through an MOCVD process, and depositing the metal on the oxide semiconductor, and the connecting of the first electrode and the second electrode may include connecting the first electrode to a first conductor provided on one side of the crystalline oxide semiconductor and connecting the second electrode to a second conductor provided on another side of the crystalline oxide semiconductor.

In another aspect of the present disclosure, there is provided a display panel including a plurality of gate lines supplied with a gate pulse, a plurality of data lines respectively supplied with data voltages, and a plurality of pixels defined by intersections of the plurality of gate lines and the plurality of data lines, wherein the plurality of pixels each include at least one the oxide TFT.

The oxide TFT according to an aspect of the present disclosure, as illustrated in FIG. 1, may include a metal insulation layer 113 including metal, a crystalline oxide semiconductor 114 on the metal insulation layer 113, a gate 118 including metal, a gate insulation layer 117 provided between the crystalline oxide semiconductor 114 and the gate 118, a first conductor 115 provided in one end of the crystalline oxide semiconductor 114, and a second conductor 116 provided in the other end of the crystalline oxide semiconductor 114.

More specifically, the oxide TFT according to an aspect of the present disclosure illustrated in FIG. 1 may include a substrate 111, a buffer 112 provided on the substrate 111, the metal insulation layer 113 which is provided on the buffer 112 and includes metal, the crystalline oxide semiconductor 114 provided on the metal insulation layer 113, the gate insulation layer 117 provided on the crystalline oxide semiconductor 114, the gate 118 provided on the gate insulation layer 117, the first conductor 115 provided in the one end of the crystalline oxide semiconductor 114, the second conductor 116 provided in the other end of the crystalline oxide semiconductor 114, an insulation layer 119 which covers the gate insulation layer 117, the gate 118, the first conductor 115, the second conductor 116, and the buffer 112, a first electrode 120 which is provided on the insulation layer 119 and is connected to the first conductor 115 through a first contact hole 122 provided in the insulation layer 199, and a second electrode 121 which is provided on the insulation layer 119 and is connected to the second conductor 116 through a second contact hole 123 provided in the insulation layer 199.

The crystalline oxide semiconductor 114 may include, for example, at least one of InGaZnO (IGZO), InZnO (IZO), InGaO (IGO), and InO which each including indium (In), gallium (Ga), zinc (Zn), and oxygen (O). The crystalline oxide semiconductor 114 may include more indium (In), and thus, may have a high mobility.

The crystalline oxide semiconductor 114 may be aligned in a direction parallel to a planar surface of the metal insulation layer 113. That is, the crystalline oxide semiconductor 114 may be aligned in one direction to have directionality. For example, the crystalline oxide semiconductor 114 may be aligned along the C-axis.

When heat is applied to the amorphous oxide semiconductor, an oxidation-reduction reaction may be performed between the amorphous oxide semiconductor and the metal. Therefore, the metal may be changed to the metal insulation layer 113, which is a nonconductor. Also, the amorphous oxide semiconductor may be aligned to have certain directionality from a surface of the metal insulation layer 113, and thus, the crystalline oxide semiconductor 114 having directionality may be formed.

That is, in an aspect of the present disclosure, the crystalline oxide semiconductor 114 may be formed to have directionality corresponding to a desired direction by using an MOCVD process. Subsequently, In, Ga, Zn, and O may be deposited by using the crystalline oxide semiconductor 114 as a seed, and thus, a height of the crystalline oxide semiconductor 114 may increase. To provide an additional description, in an aspect of the present disclosure, the crystalline oxide semiconductor 114 having a controlled crystal direction may be formed through the MOCVD process.

For example, in IGZO-based oxide semiconductors, a defect state is reduced in the C-axis-aligned crystalline layer, and reliability and mobility based on in-plane carrier transport are enhanced. That is, crystals having certain directionality may be formed in the crystalline oxide semiconductor 114, and thus, the mobility and reliability of the crystalline oxide semiconductor 114 are improved.

Particularly, in an aspect of the present disclosure, metal such as Ti or MoTi strongly reacting with oxygen may be used for forming the crystalline oxide semiconductor 114 having a controlled crystal direction. As described above, the metal may be changed to the metal insulation layer 113 through the thermal treatment process.

The gate insulation layer 117 and the gate 118 may be formed of the same material as that of a gate insulation layer applied to a general oxide semiconductor.

In an etching process of forming the gate insulation layer 117 and the gate 118, the crystalline oxide semiconductor 114 may be exposed to plasma and/or the like, and thus, the one end and the other end of the crystalline oxide semiconductor 114 may become conductive. Therefore, the first conductor 115 and the second conductor 116 may be formed.

FIGS. 2 to 4 are exemplary diagrams illustrating a method of manufacturing the oxide TFT illustrated in FIG. 1. In the following description, details which are the same as or similar to details described above with reference to FIG. 1 are omitted or will be briefly described.

The amorphous oxide semiconductor 114amay include, for example, at least one of InGaZnO (IGZO), InZnO (IZO), InGaO (IGO), and InO which each including indium (In), gallium (Ga), zinc (Zn), and oxygen (O).

Subsequently, as illustrated in FIG. 3, heat may be applied to the amorphous oxide semiconductor 114aand the metal 113a. Due to the heat, an oxidation-reduction reaction may be performed between the amorphous oxide semiconductor 114aand the metal 113a.

Due to the oxidation-reduction reaction, the metal 113amay be changed to the metal insulation layer 113, and the amorphous oxide semiconductor 114amay be changed to the crystalline oxide semiconductor 114 having directionality corresponding to one direction (for example, a direction parallel to a surface of the metal insulation layer 113).

That is, in an aspect of the present disclosure, the crystalline oxide semiconductor 114 may be formed on the metal insulation layer 113 to have directionality corresponding to a desired direction by using an MOCVD process and a thermal treatment process. Subsequently, In, Ga, Zn, and O may be further deposited on the crystalline oxide semiconductor 114 through the MOCVD process by using the crystalline oxide semiconductor 114 as a seed, and thus, a height of the crystalline oxide semiconductor 114 may increase.

Particularly, in an aspect of the present disclosure, by using a reaction of the metal 113awith oxygen, the crystalline oxide semiconductor 114 may be aligned and formed in a specific direction.

In the etching process of forming the gate insulation layer 117 and the gate 118, a region of the crystalline oxide semiconductor 114 uncovered by the gate insulation layer 117 and the gate 118 may be exposed to plasma and/or the like, and thus, may become conductive. Therefore, as illustrated in FIG. 4, the first conductor 115 may be formed in the one end of the crystalline oxide semiconductor 114, and the second conductor 116 may be formed in the other end of the crystalline oxide semiconductor 114.

Subsequently, the first contact hole 122 exposing the first conductor 115 provided in the one end of the crystalline oxide semiconductor 114 and the second contact hole 123 exposing the second conductor 116 provided in the other end of the crystalline oxide semiconductor 114 may be formed in the insulation layer 119.

Finally, the first electrode 120 connected to the first conductor 115 through the first contact hole 122 and the second electrode 121 connected to the second conductor 116 through the second contact hole 123 may be formed on the insulation layer 119. Therefore, the oxide TFT according to an aspect of the present disclosure illustrated in FIG. 1 may be manufactured.

That is, through the above-described processes, an oxide TFT including the crystalline oxide semiconductor 114 having a thickness of 150 Å or less may be manufactured. A structure illustrated in FIG. 1 may be referred to as a coplanar structure.

FIGS. 5 to 7 are other exemplary diagrams illustrating a method of manufacturing an oxide TFT according to an aspect of the present disclosure. In the following description, details which are the same as or similar to details described above with reference to FIGS. 1 to 4 are omitted or will be briefly described.

First, through the processes described above with reference to FIGS. 2 to 4, the buffer 112, the metal insulation layer 113, and the crystalline oxide semiconductor 114 may be formed on the substrate 111.

Subsequently, as illustrated in FIG. 5, another crystalline oxide semiconductor 114bmay be formed on the crystalline oxide semiconductor 114 by using the crystalline oxide semiconductor 114 as a seed.

The crystalline oxide semiconductor 114bmay be formed on the crystalline oxide semiconductor 114 through the MOCVD process, and in this case, the crystalline oxide semiconductor 114 may be used as a seed.

That is, In, Ga, Zn, and O may be further deposited on the crystalline oxide semiconductor 114 through the MOCVD process by using the crystalline oxide semiconductor 114 as a seed, and thus, a height of the crystalline oxide semiconductor 114 may increase.

Therefore, the crystalline oxide semiconductor 114bmay have the same crystalline and directionality as those of the crystalline oxide semiconductor 114. Accordingly, the crystalline oxide semiconductor 114 cannot be clearly differentiated from the crystalline oxide semiconductor 114bsubstantially.

Through the process, the height of the crystalline oxide semiconductor 114 increases. Accordingly, the height of the crystalline oxide semiconductor 114 may be variously changed.

Subsequently, the first contact hole 122 exposing the first conductor 115 provided in the one end of the crystalline oxide semiconductor 114 and the second contact hole 123 exposing

Ms.Josey

Ms.Josey

Ms.Josey

Ms.Josey