oxide tft lcd free sample

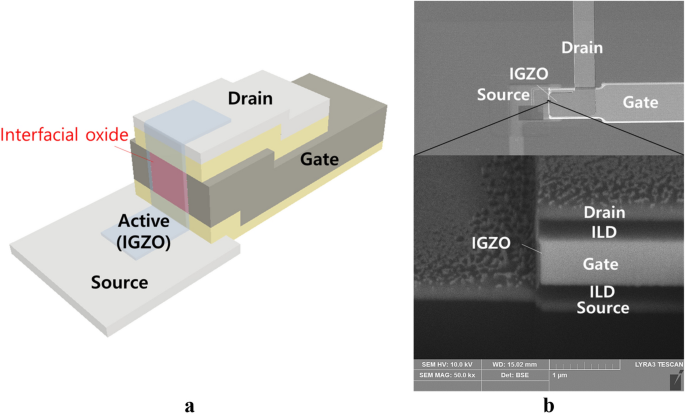

The structure of the vertical TFT with interfacial oxidation is shown in Fig. 1a. The source electrode at the bottom was made of indium tin oxide (ITO) to prevent the formation of a metal oxide insulator between the source and IGZO layer during the interfacial oxidation. The first interlayer dielectric (ILD) of SiO2 and metal gate electrode were deposited by successive sputtering, and then dry etched at one time with one photo mask. A second ILD of SiO2 and drain electrode of ITO were formed by a lift-off process, and then the gate and first ILD were dry etched by self-alignment with the drain pattern to form the vertical side wall.

After deposition of the IGZO by radio frequency (RF) magnetron sputtering, it was annealed under the oxygen atmosphere for the interfacial oxide on the side walls. As a result, the gate insulator was formed at the interface between the metal gate and IGZO active layer. The interfacial oxidation was done before the etching of the IGZO for the active layer to avoid the thick oxidation of the metal electrode which occur if the metal was not covered by the IGZO layer.

Figure 1b shows secondary electron microscope (SEM) images of the plane view and cross-sectional structure of the fabricated TFT. The vertical channel is shown between the bottom ITO electrode and top ITO electrode on the vertical side wall of the 600 nm thick gate electrode. An offset region was formed by 250 nm thick ILD layers while 600 nm channel length was defined by the 600 nm thick gate metal.

Figure 2 shows that the width of the MoOx region increases when increasing the annealing temperatures from 250 to 450 °C. At low temperatures, the interstitial oxygen can contribute to the oxidation by temperature-dependent diffusion to the interface because oxygen bond breaking from metal ions is difficult at low temperatures. The bond breaking requires much higher temperatures, so interstitial oxygen plays an important role in forming metal oxide at low temperatures. This means the oxygen ambient is very important because the oxygen continuously diffuses into the IGZO layer and migrates to the metal-IGZO interface to form metal oxide. Therefore, the adsorption and diffusion of the ambient oxygen into the IGZO layer is important for the interfacial oxidation.

To verify the effect of the oxygen atmosphere, the interfacial oxidation was examined for both oxygen and nitrogen atmospheres. Figure 3a shows HR-TEM results of the interfacial oxidation under nitrogen atmosphere, and Fig. 3b shows the result under the oxygen atmosphere. The ambient oxygen diffused into the IGZO layer by surface reaction and migrated to the IGZO layer to form metal oxide, so the oxygen atmosphere is very useful for obtaining a thicker interfacial metal-oxide for the gate insulator. The atomic percentage from the EDS analysis shows a larger oxygen ratio at the interface for the sample annealed under oxygen than that annealed under nitrogen.

The reaction of oxygen at the metal surface is important for a thicker metal-oxide at low temperatures below 400 °C For a thicker metal oxide, Ta was used instead of Mo because of its lower Gibbs free energy than that of Mo. The Gibbs free energies for MoO2 and Ta2O5 are − 533.0 and − 1911.2 kJ/mol, respectively.

Figure 4 shows the HR-TEM images of interfaces between Ta and IGZO layers for various annealing temperatures under oxygen atmosphere. The thickness of the interfacial oxide was expected to be larger in Ta than Mo due to the lower Gibbs free energy. When increasing the annealing temperatures, the interfacial oxide becomes clearer, and the thickness increases. The EDS result also matches with the HR-TEM images and shows a change of the Ta and oxygen atoms at the interface. When annealed at 450 °C anneal, the thickness of tantalum oxide was 29 nm.

Since the Ta gives thicker oxide than Mo, we choose Ta for the gate material. To avoid peel off, we keep the low thermal stress during the process. The VTFT was fabricated with interfacial oxidation between IGZO and Ta gate metal as shown in Fig. 1. The interfacial oxidation temperature was 400 °C. The transfer curves of the fabricated VTFT is shown in Fig. 5. The source-drain voltage was varied from 0.1 V to 1.0 V and the gate sweep was from − 1.0 V to 1.5 V for low-voltage operation. The thickness of the gate insulator was 15 nm, as shown in Fig. 4. The channel length was defined by the thickness of the gate metal, which was 600 nm. The channel width was defined by the photolithography and was 10 µm. The threshold voltage of the VTFT was 0.3 V, and the subthreshold slope was 0.2 V/dec. The mobility extracted from saturation region was 0.29 cm2/Vs with the gate insulator thickness of 15 nm as shown in Fig. 4. Conventional oxide VTFTs show better performances of field effect mobilities larger than 5.7 cm2/Vs

The offset is a disadvantage which should be solved to get high performance of the TFT. Since the gate metal separated source drain structure is applicable to vertical NAND flash memory, reduction of the offset effect is important. Large offset can be reduced using by decreasing the thickness of interlayer dielectric. The doping effect on the offset region is useful and can be achieved by the proper choice of the insulator which can impinge the doping elements into the IGZO layer.

For low voltage circuit applications, an inverter with the VTFT by interfacial oxidation was evaluated, as shown in Fig. 7. The channel lengths were kept the same for both the drive and load transistors, while the widths of the channel were 50 and 5 µm for the drive and load transistors, respectively.

Currents for Vds = 0.0, 0.1, 1.0 and 2.0 V are shown. Leakage currents are for the Vds = 0 V. Negative shift was observed. The process should be optimized in two aspects, one is the IGZO layer optimization for the high mobility and the other is interfacial oxide for the low leakage current and less defects. The interfacial oxidized gate insulator is the first trial and need further research to improve the characteristics of it. One drawback of the developed VTFT is the large offset length compared to the channel length which also results in a large offset AC output low. Further development on a short offset or doped offset is required.

In the proposed patterning method, these photoreactions are utilized directly for patterning. Therefore, we successfully achieved direct patterning of a simple aqueous precursor that did not contain carbon-based photosensitive additives. Selective exposure to UV light was achieved by placing a metal mask on the film during irradiation. Oxidation of the irradiated film altered its solubility, while regions not exposed to UV light were easily solved. Because the aqueous precursor was synthesized from only metal-nitrate salts and pure water, the resulting oxide film was expected to be free of carbon impurities, excepting accidental contamination during fabrication. Moreover, the easy decomposition of the nitrate-based precursor in aqueous systems leads to fewer impurities and efficient M-O-M bonds

Figure 6 shows a schematic model of the photoreaction based on the photodissociation of water molecules in the aqueous precursor followed by oxidation via thermal annealing. As indicated above, the photodissociation of water molecules and nitrate ligands under UV irradiation generated hydroxyl radicals, which acted as a strong oxidant for forming M-O bonds. Compared to the films annealed at 350 °C for 1 h, the formation of the M-O bonds after UV irradiation was insufficient in points of low intensity of the M-O bonds. However, the difference in partial oxidation between the irradiated and un-irradiated films was sufficient to achieve patterning using the etching process. Although the IGZO films after UV irradiation were not completely oxidized, the ensuing thermal annealing process enhanced the formation of metal-oxide-metal bonds and decomposed the impurities of metal ligands.

Figure 7(a–e) shows the transfer characteristics of the 18 IGZO TFTs fabricated by direct patterning and by conventional photolithography at gate voltages (Vg) ranging from −30 to 30 V and a fixed drain voltage (Vd) of 30 V. Table 1 summarizes the calculated electrical properties, including mobility (μ), ratio of maximum on-current to minimum off-current (Ion/Ioff), subthreshold swing (S.S), switch-on voltage (Von) @ Ids = 10−9 A, and hysteresis of Von. The calculated average mobility of the TFTs fabricated by direct patterning was 4.2 cm2/V·s with only a small deviation in mobility. Hysteresis in the switching behavior was also negligible. These results indicate robust uniform performance in conjunction with a high Ion/Ioff and minimal hysteresis. The ready decomposition and lack of impurities in the carbon-free aqueous precursor is believed to have contributed to the films‘ stable electrical characteristics. Direct patterning, compared to conventional photolithography, did not produce any film-degradation effects and yielded smaller deviations in the TFTs‘ electrical performance (based on mobility, Von, and hysteresis). The surface state for the back channel of oxide TFT is known as very sensitive and important layer to improve the performance of oxide TFTsS3(b) shows, the increase in OH groups in the semiconductor layers of the films were examined and compared. As Fig. S3(c) shows, unique residual peaks indicating the presence of silazanes (Si-CH3), a residue comprising photoresist material as adhesion promoter

(a) Schematic diagram of a bottom-gate, top-contact TFTs and photographic image of a fabricated TFT. Transfer characteristics for 18 IGZO TFTs fabricated by (b) the direct photoreactive patterning process and (c) conventional photolithography. Mobility histograms of the TFTs fabricated by (d) direct patterning and (e) photolithography.

Table 1 Calculated electrical parameters of solution-processed IGZO TFTs fabricated by the direct photoreactive patterning process and by conventional photolithography.

Finally, to evaluate theelectrical stability of the IGZO TFTs fabricated by direct patterning, both positive gate bias stress (PBS) and negative bias stress (NBS) were assessed. Figure 8 shows the transfer characteristics of the direct-patterned IGZO TFTs under PBS and NBS. To suppress the interaction between the air atmosphere and back channels of the TFTs, the back channels were passivated with a coating-type insulation layer, and the transfer characteristics of the TFTs at Vg ranging from −15 to 15 V were assessed at an applied drain voltage of 10 V. The stress conditions for PBS and NBS were ± 1 MV/cm, and the maximum stress time was 3,600 s at room temperature. The direct-patterned TFTs exhibited reliable switch-on voltage with ΔVon less than 1.0 V under both PBS and NBS. It is found that the aqueous solution-processed TFTs fabricated via simple direct photoreactive patterning method exhibit stable reliability. It is likely that the simple carbon-free aqueous precursor with the simple patterning process, which involves few steps without organic solvents, achieved good stability under bias stress condition.

Transfer characteristics of a direct-patterned IGZO TFT under (a) positive bias stress and (b) negative bias stress at an applied drain voltage of 10 V. (c) Changes in switch-on voltage as a function of cumulative stress time for positive and negative bias stresses.

To confirm the compatibility of direct patterning for flexible electronics, we fabricated a flexible IGZO TFTs using the direct patterning method. As Fig. 9 shows, a bottom-gate, top-contact IGZO TFT was fabricated on top a flexible polyimide substrate. The calculated mobility of the TFT was 4.8 cm2/V·s. We confirmed that the proposed direct patterning method was suitable for flexible electronics.

(a) Schematic diagram of a bottom-gate, top-contact TFTs and photographic image of a fabricated TFT on flexible polyimide substrate. (b) Transfer characteristics for IGZO TFT fabricated by the direct photoreactive patterning process. (c) Photograph of IGZO TFTs on the flexible polyimide substrate.

[1]Fortunato E., Barquinha P.,Martins R., Oxide semiconductor thin-film transistors: a review of recent advances, Adv. Mater., 2012, 24, 2945-2986.10.1002/adma.201103228Search in Google ScholarPubMed

[2]Wang Z., Nayak P.K., Caraveo-Frescas J.A., Alshareef H.N., Recent developments in p-type oxide semiconductor materials and devices, Adv. Mater., 2016, 28, 3831-3892.10.1002/adma.201503080Search in Google ScholarPubMed

[4]Petti L., Münzenrieder N., Vogt C., Faber H., Büthe L., Cantarella G., Bottacchi F., Anthopoulos T.D., Tröster G., Metal oxide semiconductor thin-film transistors for flexible electronics, Appl. Phys. Rev., 2016, 3, 021303.10.1063/1.4953034Search in Google Scholar

[5]Choi J.Y., Lee S.Y., Comprehensive review on the development of high mobility in oxide thin film transistors, J. Korean Phys. Soc., 2017, 71, 516-527.10.3938/jkps.71.516Search in Google Scholar

[7]Park J.S., Maeng W.J., Kim H.S., Park J.S., Review of recent developments in amorphous oxide semiconductor thin-film transistor devices, Thin Solid Films, 2012, 520, 1679-1693.10.1016/j.tsf.2011.07.018Search in Google Scholar

[8]Kwon J.Y., Lee D.J., Kim K.B., Review paper: Transparent amorphous oxide semiconductor thin film transistor, Electron. Mater. Lett., 2011, 7, 1-11.10.1007/s13391-011-0301-xSearch in Google Scholar

[13]Münzenrieder N., Zysset C., Petti L., Kinkeldei T., Salvatore G.A., Tröster G., Flexible double gate a-IGZO TFT fabricated on free standing polyimide foil, Solid-State Electron., 2013, 84, 198-204.10.1016/j.sse.2013.02.025Search in Google Scholar

[15]Chong E., Kim B., Lee S.Y., Reduction of channel resistance in amorphous oxide thin-film transistorswith buried layer, IOP Conf. Series: Mater. Sci. Eng., 2012, 34, 012005.10.1088/1757-899X/34/1/012005Search in Google Scholar

[25]Geng D., Kang D.H., Seok M.J., Mativenga M., Jang J., High-speed and low-voltage-driven shift register with self-aligned coplanar a-IGZO TFTs, IEEE Electron Device Lett., 2012, 33, 1012-1014.10.1109/LED.2012.2194133Search in Google Scholar

[30]Dehuff N.L., Kettenring E.S., Hong D., Chiang H.Q., Wager J.F., Hoffman R.L., Park C.H., Keszler D.A., Transparent thin-film transistors with zinc indium oxide channel layer, J. Appl. Phys., 2005, 97, 0645050.10.1063/1.1862767Search in Google Scholar

[34]Togo A., Oba F., Tanaka I., Tatsumi K., First-principles calculations of native defects in tin monoxide, Phys. Rev., B 2006, 74, 195128.10.1103/PhysRevB.74.195128Search in Google Scholar

[35]Ogo Y., Hiramatsu H., Nomura K., Yanagi H., Kamiya T., Kimura M., Hirano M., Hosono H., Tin monoxide as an s-orbital-based p-type oxide semiconductor: Electronic structures and TFT application, Physica Status Solidi (a), 2009, 206, 2187-2191.10.1002/pssa.200881792Search in Google Scholar

[43]Ogo Y., Hiramatsu H., Nomura K., Yanagi H., Kamiya T., Hirano M., Hosono H., P-channel thin-film transistor using p-type oxide semiconductor, SnO. Appl. Phys. Lett., 2008, 93, 032113.10.1063/1.2964197Search in Google Scholar

[46]Greiner M.T., Lu Z.H., Thin-film metal oxides in organic semiconductor devices: their electronic structures, work functions and interfaces, NPG Asia Mater., 2013, 5, e55.10.1038/am.2013.29Search in Google Scholar

[47]Lany S., Osorio-Guillén J., Zunger A., Origins of the doping asymmetry in oxides: hole doping in NiO versus electron doping in ZnO, Phys. Rev. B, 2007, 75, 241203.10.1103/PhysRevB.75.241203Search in Google Scholar

[54]Kim S.Y., Ahn C.H., Lee J.H., Kwon Y.H., Hwang S., Lee J.Y., Cho H.K., P-channel oxide thin film transistors using solution-processed copper oxide, ACS Appl. Mater. Interfaces, 2013, 5, 2417-2421.10.1021/am302251sSearch in Google ScholarPubMed

[55]Chen Z., Xiao X., Shao Y., Meng W., Zhang S., Yue L., Xie L., Zhang P., Lu H., Zhang S., Fabrication of p-type copper oxide thin-film transistors at different oxygen partial pressure, 2014 12th IEEE Int’l Conference on Solid-State and Integrated Circuit Technology (ICSICT), Guilin, 2014, 1-3.10.1109/ICSICT.2014.7021451Search in Google Scholar

[56]Maeng W., Lee S.H., Kwon J.D., Park J., Park J.S., Atomic layer deposited p-type copper oxide thin films and the associated thin film transistor properties, Ceram. Int., 2016, 42, 5517-5522.10.1016/j.ceramint.2015.12.109Search in Google Scholar

[57]Liu A., Liu G., Zhu H., Song H., Shin B., Fortunato E., Martins R., Shan F., Water-induced scandium oxide dielectric for low-operating voltage n- and p-type metal-oxide thin-film transistors, Adv. Funct. Mater., 2015, 25, 7180-7188.10.1002/adfm.201502612Search in Google Scholar

[58]Liu A., Nie S., Liu G., Zhu H., Zhu C., Shin B., Fortunato E.,Martins R., Shan F., In situ one-step synthesis of p-type copper oxide for low-temperature, solution-processed thin-film transistors, J. Mater. Chem. C, 2017, 5, 2524-2530.10.1039/C7TC00574ASearch in Google Scholar

[59]Jung T.S., Lee H., Park S.P., Kim H.J., Lee J.H., Kim D., Kim H.J., Enhancement of switching characteristic for p-type oxide semiconductors using hypochlorous acid, ACS Appl.Mater. Interfaces, 2018, 10, 32337-32343.10.1021/acsami.8b10390Search in Google ScholarPubMed

[62]Fortunato E., Martins R., Where science fiction meets reality? With oxide semiconductors! Phys. Status. Solidi-R., 2011, 5, 336-339.10.1002/pssr.201105246Search in Google Scholar

[63]Yabuta H., Kaji N., Hayashi R., Kumomi H., Nomura K., Kamiya T., Hirano M., Hosono H., Sputtering formation of p-type SnO thin-film transistors on glass toward oxide complimentary circuits, Appl. Phys. Lett., 2010, 97,072111.10.1063/1.3478213Search in Google Scholar

[64]Nomura K., Kamiya T., Hosono H., Ambipolar oxide thin-film transistor, Adv. Mater., 2011, 23, 3431-3434.10.1002/adma.201101410Search in Google ScholarPubMed

[65]Okamura K., Nasr B., Brand R.A., Hahn H., Solution-processed oxide semiconductor SnO in p-channel thin-film transistors, J. Mater. Chem., 2012, 22, 4607-4610.10.1039/c2jm16426dSearch in Google Scholar

[66]Caraveo-Frescas J.A., Nayak P.K., Al-Jawhari H.A., Granato D.B., Schwingenschlögl U., Alshareef H.N., Record mobility in transparent p-type tin monoxide films and devices by phase engineering, ACS Nano, 2013, 7, 5160-5167.10.1021/nn400852rSearch in Google ScholarPubMed

[67]Lee H.N., Song B.J., Park J.C., Fabrication of p-channel amorphous tin oxide thin-film transistors using a thermal evaporation process, J. Display Technol., 2014, 10, 288-292.10.1109/JDT.2014.2298862Search in Google Scholar

[70]Chen P.C., Chiu Y.C., Zheng Z.W., Cheng C.H., Wu Y.H., P-type tinoxide thin film transistors for blue-light detection application, Phys. Status. Solidi-R., 2016, 10, 919-923.10.1002/pssr.201600287Search in Google Scholar

[71]Chen P.C., Wu Y.H., Zheng Z.W., Chiu Y.C., Cheng C.H., Yen S.S., Hsu H.H., Chang C.Y., Bipolar conduction in tin-oxide semiconductor channel treated by oxygen plasma for low-power thin-film transistor application, J. Display Technol., 2016, 12, 224-227.10.1109/JDT.2015.2457439Search in Google Scholar

[72]Chiu Y.C., Chen P.C., Chang S.L., Zheng Z.W., Cheng C.H., Liou G.L., Kao H.L., Wu Y.H., Chang C.Y., Channel modification engineering by plasma processing in tin-oxide thin film transistor: experimental results and first-principles calculation, ECS J. Solid. State. SC., 2017, 6, Q53-Q57.10.1149/2.0251704jssSearch in Google Scholar

[73]Chen P.C., Chiu Y.C., Zheng Z.W., Lin M.H., Cheng C.H., Liou G.L., Hsu H.H., Kao H.L., Fast low-temperature plasma process for the application of flexible tin-oxide-channel thin film transistors, IEEE Trans. Nanotechnol., 2017, 16, 876-879.10.1109/TNANO.2017.2719946Search in Google Scholar

[74]Chen P.C., Chiu Y.C., Zheng Z.W., Cheng C.H., Wu Y.H., Influence of plasma fluorination on p-type channel tin-oxide thin film transistors, J. Alloys Comp., 2017, 707, 162-166.10.1016/j.jallcom.2016.11.294Search in Google Scholar

[75]Rajshekar K., Hsu H.H., Kumar K.U.M., Sathyanarayanan P., Velmurugan V., Cheng C.H., Kannadassan D., Effect of plasma fluorination in p-type SnO TFTs: experiments, modeling, and simulation, IEEE T. Electron. Dev., 2019, 66, 1314-1321.10.1109/TED.2019.2895042Search in Google Scholar

[76]Chen P.C., Chiu Y.C., Liou G.L., Zheng Z.W., Cheng C.H., Wu Y.H., Performance enhancements in p-type Al-doped tin-oxide thin film transistors by using fluorine plasma treatment, IEEE Electron Device Lett., 2017, 38, 210-212.10.1109/LED.2016.2646378Search in Google Scholar

[77]Bae S.D., Kwon S.H., Jeong H.S., Kwon H.I., Demonstration of high-performance p-type tin oxide thin-film transistors using argon-plasma surface treatments, Semicond. Sci. Technol, 2017, 32, 075006.10.1088/1361-6641/aa72b8Search in Google Scholar

[80]Barros R., Saji K.J., Waerenborgh J.C., Barquinha P., Pereira L., Carlos E.,Martins R., Fortunato E., Role of structure and composition on the performances of p-type tin oxide thin-film transistors processed at low-temperatures, Nanomaterials 2019, 9, 320.10.3390/nano9030320Search in Google ScholarPubMedPubMed Central

[83]Liu S., Liu R., Chen Y., Ho S., Kim J.H., So F., Nickel oxide hole injection/transport layers for efficient solution-processed organic light-emitting diodes, Chem. Mater., 2014, 26, 4528-4534.10.1021/cm501898ySearch in Google Scholar

[87]Hu H., Zhu J., Chen M., Guo T., Li F., Inkjet-printed p-type nickel oxide thin-film transistor, Appl. Surf. Sci., 2018, 441, 295-302.10.1016/j.apsusc.2018.02.049Search in Google Scholar

[88]Lee H.N., Kyung J., Sung M.C., Kim D.Y., Kim S.T., Oxide TFT with multilayer gate insulator for backplane of AMOLED device, J. Soc. Inf. Display., 2008, 16, 265-272.10.1889/1.2841860Search in Google Scholar

[91]Na J.H., Kitamura M., Arakawa Y., Organic/inorganic hybrid complementary circuits based on pentacene and amorphous indium gallium zinc oxide transistors, Appl. Phys. Lett., 2008, 93, 213505.10.1063/1.3039779Search in Google Scholar

[92]Ou C.W., Dhananjay, Ho Z.Y., Chuang Y.C., Cheng S.S., Wu M.C., Ho K.C., Chu C.W., Anomalous p-channel amorphous oxide transistors based on tin oxide and their complementary circuits, Appl. Phys. Lett., 2008, 92, 122113.10.1063/1.2898217Search in Google Scholar

[94]Nayak P.K., Caraveo-Frescas J.A., Wang Z., Hedhili M.N., Wang Q.X., Alshareef H.N., Thin film complementary metal oxide semiconductor (CMOS) device using a single-step deposition of the channel layer, Sci. Rep., 2014, 4, 4672.10.1038/srep04672Search in Google ScholarPubMedPubMed Central

[95]Chiu I.C., Li Y.S., Tu M.S., Cheng I.C., Complementary oxide-semiconductor-based circuits with n-channel ZnO and p-channel SnO thin-film transistors, IEEE Electron Device Lett., 2014, 35, 1263-1265.10.1109/LED.2014.2364578Search in Google Scholar

[96]Li Y.S., He J.C., Hsu S.M., Lee C.C., Su D.Y., Tsai F.Y., Cheng I.C., Flexible Complementary Oxide-Semiconductor-Based Circuits Employing n-Channel ZnO and p-Channel SnO Thin-Film Transistors, IEEE Electron Device Lett., 2016, 37, 46-49.10.1109/LED.2015.2501843Search in Google Scholar

[97]Dindar A., Kim J.B., Fuentes-Hernandez C., Kippelen B., Metal-oxide complementary inverters with a vertical geometry fabricated on flexible substrates, Appl. Phys. Lett., 2011, 99, 172104.10.1063/1.3656974Search in Google Scholar

[98]Martins R.F.P., Ahnood A., Correia N., Pereira L.M.N.P., Barros R., Barquinha P.M.C.B., Costa R., Ferreira I.M.M., Nathan A., Fortunato E.E.M.C., Recyclable, flexible, low-power oxide electronics, Adv. Funct. Mater., 2013, 23, 2153-2161.10.1002/adfm.201202907Search in Google Scholar

[102]Li Y., Zhang J., Yang J., Yuan Y., Hu Z., Lin Z., Song A., Xin Q., Complementary integrated circuits based on n-type and p-type oxide semiconductors for applications beyond flat-panel displays, IEEE T. Electron. Dev., 2019, 66, 950-956.10.1109/TED.2018.2887270Search in Google Scholar

[103]Martins R., Nathan A., Barros R., Pereira L., Barquinha P., Correia N., Costa R., Ahnood A., Ferreira I., Fortunato E., Complementary metal oxide semiconductor technology with and on paper, Adv. Mater., 2011, 23, 4491-4496.10.1002/adma.201102232Search in Google ScholarPubMed

[104]Wang Z., Al-Jawhari H.A., Nayak P.K., Caraveo-Frescas J.A., Wei N., Hedhili M.N., Alshareef H.N., Low temperature processed complementary metal oxide semiconductor (CMOS) device by oxidation effect from capping layer, Sci. Rep., 2015, 5, 9617.10.1038/srep09617Search in Google Scholar

[110]Estrela P., Migliorato P., Chemical and biological sensors using polycrystalline silicon TFTs, J. Mater. Chem., 2007, 17, 219-224.10.1039/B612469KSearch in Google Scholar

[113]Dong L., Yue R., Liu L., Xia S., Design and fabrication of single-chip a-Si TFT-based uncooled infrared sensors, Sensor. Actuat. A-Phys., 2004, 116, 257-263.10.1016/j.sna.2004.04.030Search in Google Scholar

[118]Tixier-Mita A., Ségard B., Kim Y., Matsunaga Y., Fujita H., Toshiyoshi H., TFT display panel technology as a base for biological cells electrical manipulation - application to dielectrophoresis, IEEE International Conference on Micro Electro Mechanical Systems (MEMS), Estoril, 2015, 354-357.10.1109/MEMSYS.2015.7050962Search in Google Scholar

[122]Wang W., Xu G., Chowdhury M.D.H., Wang H., Um J.K., Ji Z., Gao N., Zong Z., Bi C., Lu C., Lu N., Banerjee W., Feng J., Li L., Kadashchuk A., Jang J., Liu M., Electric field modified Arrhenius description of charge transport in amorphous oxide semiconductor thin film transistors, Phys. Rev. B, 2018, 98, 245308.10.1103/PhysRevB.98.245308Search in Google Scholar

[125]Nomura K., Recent progress of oxide-semiconductor-based p-channel TFTs, SID Symposium Digest of Technical Papers, 2015, 591-594.10.1002/sdtp.10167Search in Google Scholar

[126]Lu N., Jiang W., Wu Q., Geng D., Li L., Liu M., A review for compact model of thin-film transistors (TFTs), Micromachines, 2018, 9, 599.10.3390/mi9110599Search in Google ScholarPubMedPubMed Central

From the MOSFET, the TFT was born. The TFT varies from standard MOSFETs, or bulk MOSFETs, because, as the name implies, it uses thin films. The TFT began a new era of electronics. In 1968, just six years after the first TFT development, Bernard J. Lechner of RCA shared his idea of the TFT Liquid Crystal Display (LCD), something that would boom in popularity in our modern times. The TFT LCD was then first created in 1973 at the Westinghouse Research Laboratories. These LCDs were composed of pixels controlled by transistors. In FETs, substrates were just the semiconductor material, but in manufacturing TFT LCDs, glass substrates were used so that the pixels could be displayed.

But that was not the end of TFT developments. Soon after, in 1974, T. Peter Brody, one of the developers of the TFT LCD, and Fang-Chen Luo created the first active-matrix LCD (AM LCD). An active matrix controls each pixel individually, meaning that each pixel’s respective TFT had its signal actively preserved. This opened doors to better performance and speed as displays became more complex.

Though TFTs can use a variety of materials for their semiconductor layers, silicon has become the most popular, creating the silicon-based TFT, abbreviated as Si TFT. As a semiconductor device, the TFT, as well as all FETs, use solid-state electronics, meaning that electricity flows through the structure of the semiconductor layer rather than vacuum tubes.

Due to the variety in silicon’s possible structures, the Si TFT’s characteristics can vary as well. The most common form is amorphous silicon (A-Si), which is deposited during the first step of the semiconductor fabrication process onto the substrate in low temperatures. It is most usable when hydrogenated into the form A-Si:H. This then significantly alters the properties of A-Si; without the hydrogen, the material struggles with doping (the introduction of impurities to increase mobility of charges); in the form A-Si:H, however, the semiconductor layer becomes much more photoconductive and dopable. The A-Si:H TFT was first developed in 1979 which is stable at room temperature and became the best option for AM LCDs which consequently began rising in popularity after this breakthrough.

The biggest difference between these forms, notably A-Si and poly-Si, is that charge carriers are much more mobile and the material is much more stable when it comes to using poly-Si over A-Si. When creating complicated and high-speed TFT-based displays, poly-Si’s characteristics allow for this. Yet, A-Si is still very important due to its low-leakage nature, meaning that leakage current is not lost as heavily when a dielectric insulator is not totally non-conductive.

Several years later, another development was made in 2012 in the form of indium gallium zinc oxide (IGZO) which allowed for a more powerful display in terms of refresh rates and more efficiency in terms of power consumption. This semiconducting material, as stated in the name, uses indium, gallium, zinc, and oxygen. Though it is a form of zinc oxide (ZnO), the addition of indium and gallium allows this material to be deposited in a uniform amorphous phase but also maintaining the oxide’s high carrier mobility.

As TFTs began to increase their presence in display technology, transparent semiconductors and electrodes became more appealing to the manufacturers. Indium tin oxide (ITO) is an example of a popular transparent oxide used for its appearance, good conductivity, and ease of deposition.

Research of the TFT with different materials has led to the application of threshold voltage, or how much voltage is needed to turn on the device. This value is greatly dependent on thickness and choice of the oxide. When it comes to the oxide, this relates back to the idea of leakage current. With thinner layers and certain types of oxide, the leakage current may be greater, but this in turn could lower threshold voltage, as leakage into the device will also increase. In order to tap into the TFT’s potential for low power consumption, the lower the threshold voltage, the better the device’s appeal.

Another branch of development that stemmed from the TFT is that of organic TFTs (OTFT). First created in 1986, OTFTs usually use solution-casting of polymers, or macromolecules. This device made people hesitant, as it tended to have a slow carrier mobility, meaning slow response times. However, researchers have carried out experimentation with the OTFT because it has potential to be applied to displays different from those that traditional TFTs are used for, such as flexible, plastic displays. This research still continues today. With its simpler processing than traditional silicon technology, the OTFT holds much potential for modern day and future technologies.

The oxide semiconductor has always to my mind been the interesting middle ground in the display industry. But to date, it has been mastered by relatively few players Sharp and LGD come to mind) as the physics of the device are distinctly different to amorphous silicon (a-Si).

(For those that are new to this subject, backplanes based on oxide transistors have fewer masks than LTPS (typically between 4 and 8 compared to 11+) and higher mobility than a-Si (meaning smaller, faster transistors, larger aperture ratios). There are some additional benefits, such as some of the capabilities to replicate driving and multiplexing functionality in the borders of the display and reduce the needed semiconductor ICs. Oxides also have low leakage current. However, there has not been quite enough performance to be a possible LTPS replacement or superior backplane for emissive technologies).

Up to now the oxide semiconductor has been found in WOLED TVs (at LGD) with almost 13 million m² of capacity (2022) and then in pockets of applications. For example, it has been used for higher resolution iPads. The oxide market is perhaps around 15-20 million m² or a pretty distant third place for oxide behind the leader amorphous silicon (>250 million m²) and low temperature polysilicon, LTPS (30 million m²).

However, the demand trajectory for a mid-performance semiconductor is now moving upwards, with two additional applications. And as “demand” increases, then the industry will look for new sources of high-performance oxide at a technology level.

The new drivers of demand are both from Samsung. The first is the long announced QD OLED technology for TV and monitors which is beginning to ramp as we speak from November 2021 and was shown privately at CES 2022. This new technology plans to compete alongside WOLED TV but is based on fluorescent blue emitters (a 3-layer blue stack), and potentially 6 million m² (or 90k/month Gen 8 within a fairly short horizon and the potential for a Gen 10 later). This QD OLED technology needs an oxide backplane. Large panel emissive displays can have narrower borders and higher frame rates with better performing oxide.

For now, DSCC is talking about demand changes nearer to the 5% level over the near term but this is still roughly $15 billion+ in capital and 7.5 million m² in new oxide backplanes (based on typical over building assumptions) being installed.

The supply of oxide then could rapidly move from about 15 million m² today to more than 38 million m² (20% CAGR) and more as producers prove out the role of IT OLED panels based on a lower cost backplane than today’s LTPS and Samsung tries to compete with LGD WOLED. BOE and LGD will also aim to grow the space.

And as a really exciting thought experiment, should IT panels eventually mirror today’s smartphone and move to say 50% of units as OLED then this could be 5x as big taking oxide into the > 100 million m² range in terms of installed capacity.

Amorphyx has been working on its own approach to high performance oxide, with mobility in excess of 60 cm²/Vs and a path to higher. Its technology is based on a proprietary amorphous metal gate with a thin high-k dielectric gate insulator. The only process change is a slight increase in PVD in the line and the use of reactive sputter. Their process can work with any player to transfer the technology.

This is a new adder to the oxide manufacturing and we believe is largely additive to other approaches that players may use to try to augment oxide mobility. Amorphyx believe that the interest in oxide development will spread around the industry and players will look for ways to be competitive.

Overall, this is the time for oxide to climb the rankings in importance in the display industry. If oxide does become well entrenched into FMM OLED for Gen 8, then will this then be proof enough that it can play in Gen 6 mobile applications too and displace LTPS. These are interesting times for oxide developments. (IH)

Advancements in thin-film transistor (TFT) technology have extended to electronics that can withstand extreme bending or even folding. Although the use of ultrathin plastic substrates has achieved considerable advancement towards this end, free-standing ultrathin plastics inevitably suffer from mechanical instability and are very difficult to handle during TFT fabrication. Here, in addition to the use of a 1.5

Advancements in thin-film transistor (TFT)-based electronics for display and sensor applications have recently extended to electronics on plastic substrates that can be folded, rolled or crumpled up without cracking the screen or even degrading functionality,2,3,4,5,6,7,8,9. These deformable electronics can be applied to portable devices or non-flat, curvilinear surfaces in pipelines, automobiles and other related areas. TFT displays with no bezels can be achieved when the driving electronics that are usually located at the peripherals of the display screen (i.e. the bezel) can be folded to occupy the side edges or even back side of the display device. Foldability will also enable easy transportation and storage while not in use. For the final product to be flexible, however, the substrate on which the electronics are built should also be flexible

In this paper, we use ultrathin plastic substrates for extreme bending capabilities, and we also deposit a second ultrathin plastic film of similar thickness on top of the TFT devices to ensure that the devices are located close to the neutral bending plane of the two plastics for minimum strain. Additionally, we also embed a mixture of graphene oxide (GO) and carbon nanotubes (CNTs) into the bottom surface of the ultrathin substrate for mechanical support and reduction of electrostatic discharge (ESD) damage. The material used as the ultrathin substrate and ultrathin top film is a solution processed 1.5-thick PI film, given the many advantages of PI compared to other plastics such as PET or PEN, which include higher glass transition temperature, lower coefficient of thermal expansion (CTE), higher chemical resistance, and higher processing temperature. Consequently, the PI allows fabrication process temperatures as high as 300

(a) Formation of a CNT/GO release layer on carrier glass by spin coating. (b) Formation of PI substrate by spin coating. (c) Formation of a gas barrier, composed five alternating SiO2 and SiNx layers deposited by plasma-enhanced chemical vapor deposition. (d) TFT formation. (e) Formation of a top PI film (1.5

The fabrication process of the a-IGZO NP TFTs is depicted in Fig. 1 and details of the materials can be found in the Methods Section. The oxide TFTs on plastic/glass can be easily detached mechanically, without the use of expensive lasers, because of the existence of the CNT/GO layerFig. 1h,i, respectively. The typical performance of a-IGZO TFTs fabricated without and with the top NP PI film are shown in Fig. 2a,b. In each case, TFT characteristics, before and after detachment from the carrier glass, are provided. In both cases, the TFT’s VON shifts towards the negative gate voltage (VGS) direction after detachment. However, the shift is much smaller for the NP TFTs. For TFTs fabricated without the top NP PI film, the μFE increases from 22

(a,b) Transfer characteristics and field-effect mobility, before and after detachment of a-IGZO TFTs (a) without and (b) with the top neutral plane PI film. (c)Transmittance measurements and (insets) photographs of a substrate with and without TFT devices after detachment from carrier glass. (d) Cross sectional scanning electron microscope (SEM) image of the substrate before detachment from carrier glass. (e) SEM image of the bottom surface of the PI substrate after detachment from carrier glass.

The negative VON shift (ΔVON) that occurs after detachment from carrier glass is related to the mechanical strain during the detachment process. Channel conductivity may increase after the application of mechanical strain to the TFT, which may result in a negative shift of VON after detachment. It is previously reported that mechanical strain causes an increase (in the case of tensile strain) in donor concentration, which causes the Fermi level to shift closer to the conduction band and, therefore, a negative shift of VON

To evaluate bending stability of the a-IGZO TFTs, samples are wound to cylinders of decreasing radius and devices tested while bending. Starting from a cylinder with a radius of 3

To further evaluate the effect of the top PI film on the bending stability of the TFTs, the samples are exposed to repeated extreme bending cycles to a radius of 0.25

Performance degradation (before breakdown) characterized by negative ΔVON, such as that experienced by the TFTs without the NP PI after detachment from glass (Fig. 2a), has been explained to be the result of tensile strain-induced increase in channel conductivity that is brought about by an increase in the donor concentrationFig. 3(e,f)). There is no visible evidence of cracks in TFTs that can still operate, despite them having gone through negative ΔVON. Several TFTs are tested across 6 inch by 6 inch substrates to investigate device uniformity. Figure 3i,j show respectively the results for the TFTs without the NP top PI film and the NP TFTs. After 5000 bending cycles, a large number of TFTs without the top PI film broke down (Supplementary Figure S2a), whereas none of the NP TFTs broke down after 5,000 bending cycles (Supplementary Figure S1b). A negative ΔVON

In addition, the NP TFTs also remain mechanically stable after being transferred to the stretchable PDMS substrate. Here, PDMS is a preferred choice, given that it is transparent and can be rolled, twisted and stretched (Fig. 4a). Note here that the NP TFTs are transferred onto the PDMS film in the form of islands, in order to achieve partial stretchability in the PDMS-only area (Supplementary Figure S3). The NP TFTs are unstretchable. Figure 4b and c show respectively an unstretched and a stretched sample. The direction of the stretch is parallel to the TFT channel. A sample that is initially 40

Stretching Test: (a) Optical micrograph of PDMS films in the (left) flat and (right) rolled and twisted conditions. (b,c) Image of neutral plane TFTs after being transferred to the PDMS film (b) before and (c) while being stretched in the direction parallel to the TFT channel. Extended length of the PDMS film is 10

The TFT fabrication process is initiated by the deposition of Mo by sputtering on top of the gas barrier and its patterning to form the gate electrode. This is followed by the deposition of a 250

TFTs are characterized in a black box using an Agilent 4156C precision semiconductor parameter analyzer. TFTs’ current-voltage characteristics are measured in dark and at room temperature. The field-effect mobility (μFE) and subthreshold swing (SS) are extracted from the conventional metal-oxide-semiconductor field effect transistor (MOSFET) equationFE, derived from transconductance (gM), ∂IDS/∂VGS, is given by μFE

The extreme bending machine can bend the device from −120 to 120 degrees. There are clamps which hold the device in place. The clamps are fixed by magnets to avoid damage to the TFTs. The distance between two clamps is 0.5

How to cite this article: Kim, Y.-H. et al. Highly Robust Neutral Plane Oxide TFTs Withstanding 0.25 mm Bending Radius for Stretchable Electronics. Sci. Rep. 6, 25734; doi: 10.1038/srep25734 (2016).

Author Contributions Y.-H.K. and E.L. carried out the TFT fabrication and characterization and J.G.U. and M.M. measured SEM images and J. Jang initiated the idea and checked the results. All the authors contributed to writing the manuscript.

et al.. Defect generation in amorphous-indium-gallium-zinc-oxide thin film transistors by positive bias stress at elevated temperature. Appl. Phys. Lett.

et al.. Remarkable changes in interface O vacancy and metal-oxide bonds in amorphous indium-gallum-zinc –oxide thin-film transistors by long time annealing at 250

A thin-film-transistor liquid-crystal display (TFT LCD) is a variant of a liquid-crystal display that uses thin-film-transistor technologyactive matrix LCD, in contrast to passive matrix LCDs or simple, direct-driven (i.e. with segments directly connected to electronics outside the LCD) LCDs with a few segments.

In February 1957, John Wallmark of RCA filed a patent for a thin film MOSFET. Paul K. Weimer, also of RCA implemented Wallmark"s ideas and developed the thin-film transistor (TFT) in 1962, a type of MOSFET distinct from the standard bulk MOSFET. It was made with thin films of cadmium selenide and cadmium sulfide. The idea of a TFT-based liquid-crystal display (LCD) was conceived by Bernard Lechner of RCA Laboratories in 1968. In 1971, Lechner, F. J. Marlowe, E. O. Nester and J. Tults demonstrated a 2-by-18 matrix display driven by a hybrid circuit using the dynamic scattering mode of LCDs.T. Peter Brody, J. A. Asars and G. D. Dixon at Westinghouse Research Laboratories developed a CdSe (cadmium selenide) TFT, which they used to demonstrate the first CdSe thin-film-transistor liquid-crystal display (TFT LCD).active-matrix liquid-crystal display (AM LCD) using CdSe TFTs in 1974, and then Brody coined the term "active matrix" in 1975.high-resolution and high-quality electronic visual display devices use TFT-based active matrix displays.

The circuit layout process of a TFT-LCD is very similar to that of semiconductor products. However, rather than fabricating the transistors from silicon, that is formed into a crystalline silicon wafer, they are made from a thin film of amorphous silicon that is deposited on a glass panel. The silicon layer for TFT-LCDs is typically deposited using the PECVD process.

Polycrystalline silicon is sometimes used in displays requiring higher TFT performance. Examples include small high-resolution displays such as those found in projectors or viewfinders. Amorphous silicon-based TFTs are by far the most common, due to their lower production cost, whereas polycrystalline silicon TFTs are more costly and much more difficult to produce.

The twisted nematic display is one of the oldest and frequently cheapest kind of LCD display technologies available. TN displays benefit from fast pixel response times and less smearing than other LCD display technology, but suffer from poor color reproduction and limited viewing angles, especially in the vertical direction. Colors will shift, potentially to the point of completely inverting, when viewed at an angle that is not perpendicular to the display. Modern, high end consumer products have developed methods to overcome the technology"s shortcomings, such as RTC (Response Time Compensation / Overdrive) technologies. Modern TN displays can look significantly better than older TN displays from decades earlier, but overall TN has inferior viewing angles and poor color in comparison to other technology.

The transmittance of a pixel of an LCD panel typically does not change linearly with the applied voltage,sRGB standard for computer monitors requires a specific nonlinear dependence of the amount of emitted light as a function of the RGB value.

Less expensive PVA panels often use dithering and FRC, whereas super-PVA (S-PVA) panels all use at least 8 bits per color component and do not use color simulation methods.BRAVIA LCD TVs offer 10-bit and xvYCC color support, for example, the Bravia X4500 series. S-PVA also offers fast response times using modern RTC technologies.

TFT dual-transistor pixel or cell technology is a reflective-display technology for use in very-low-power-consumption applications such as electronic shelf labels (ESL), digital watches, or metering. DTP involves adding a secondary transistor gate in the single TFT cell to maintain the display of a pixel during a period of 1s without loss of image or without degrading the TFT transistors over time. By slowing the refresh rate of the standard frequency from 60 Hz to 1 Hz, DTP claims to increase the power efficiency by multiple orders of magnitude.

Due to the very high cost of building TFT factories, there are few major OEM panel vendors for large display panels. The glass panel suppliers are as follows:

External consumer display devices like a TFT LCD feature one or more analog VGA, DVI, HDMI, or DisplayPort interface, with many featuring a selection of these interfaces. Inside external display devices there is a controller board that will convert the video signal using color mapping and image scaling usually employing the discrete cosine transform (DCT) in order to convert any video source like CVBS, VGA, DVI, HDMI, etc. into digital RGB at the native resolution of the display panel. In a laptop the graphics chip will directly produce a signal suitable for connection to the built-in TFT display. A control mechanism for the backlight is usually included on the same controller board.

The low level interface of STN, DSTN, or TFT display panels use either single ended TTL 5 V signal for older displays or TTL 3.3 V for slightly newer displays that transmits the pixel clock, horizontal sync, vertical sync, digital red, digital green, digital blue in parallel. Some models (for example the AT070TN92) also feature input/display enable, horizontal scan direction and vertical scan direction signals.

New and large (>15") TFT displays often use LVDS signaling that transmits the same contents as the parallel interface (Hsync, Vsync, RGB) but will put control and RGB bits into a number of serial transmission lines synchronized to a clock whose rate is equal to the pixel rate. LVDS transmits seven bits per clock per data line, with six bits being data and one bit used to signal if the other six bits need to be inverted in order to maintain DC balance. Low-cost TFT displays often have three data lines and therefore only directly support 18 bits per pixel. Upscale displays have four or five data lines to support 24 bits per pixel (truecolor) or 30 bits per pixel respectively. Panel manufacturers are slowly replacing LVDS with Internal DisplayPort and Embedded DisplayPort, which allow sixfold reduction of the number of differential pairs.

Kawamoto, H. (2012). "The Inventors of TFT Active-Matrix LCD Receive the 2011 IEEE Nishizawa Medal". Journal of Display Technology. 8 (1): 3–4. Bibcode:2012JDisT...8....3K. doi:10.1109/JDT.2011.2177740. ISSN 1551-319X.

K. H. Lee; H. Y. Kim; K. H. Park; S. J. Jang; I. C. Park & J. Y. Lee (June 2006). "A Novel Outdoor Readability of Portable TFT-LCD with AFFS Technology". SID Symposium Digest of Technical Papers. AIP. 37 (1): 1079–82. doi:10.1889/1.2433159. S2CID 129569963.

Ms.Josey

Ms.Josey

Ms.Josey

Ms.Josey